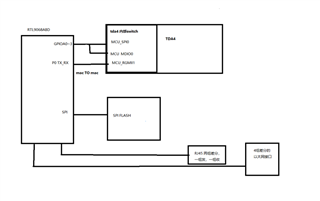

1. This is the block diagram of TDA4 and RTL9068 connection.

2.The sdk version is 8.6

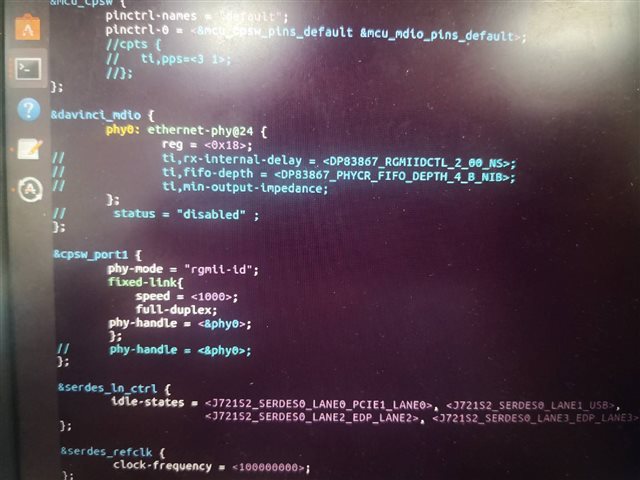

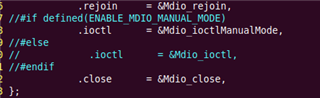

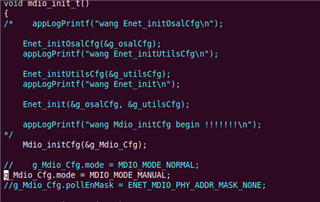

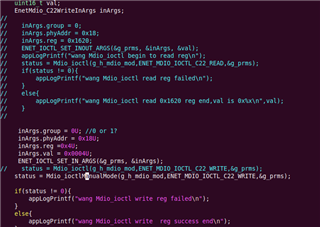

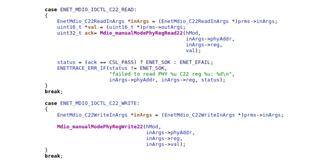

3. Modify the code as follows:

--- a/board-support/u-boot/arch/arm/dts/k3-j721s2-common-proc-board.dts

+++ b/board-support/u-boot/arch/arm/dts/k3-j721s2-common-proc-board.dts

@@ -363,20 +363,27 @@

&mcu_cpsw {

pinctrl-names = "default";

pinctrl-0 = <&mcu_cpsw_pins_default &mcu_mdio_pins_default>;

};

-&davinci_mdio {

- phy0: ethernet-phy@0 {

- reg = <0>;

- ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

- ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

- ti,min-output-impedance;

- };

-};

+//&davinci_mdio {

+// phy0: ethernet-phy@0 {

+// reg = <0>;

+// ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

+// ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

+// ti,min-output-impedance;

+// };

+//};

&cpsw_port1 {

phy-mode = "rgmii-rxid";

- phy-handle = <&phy0>;

+ fixed-link {

+ speed = <1000>;

+ full-duplex;

+ };

+// phy-handle = <&phy0>;

};

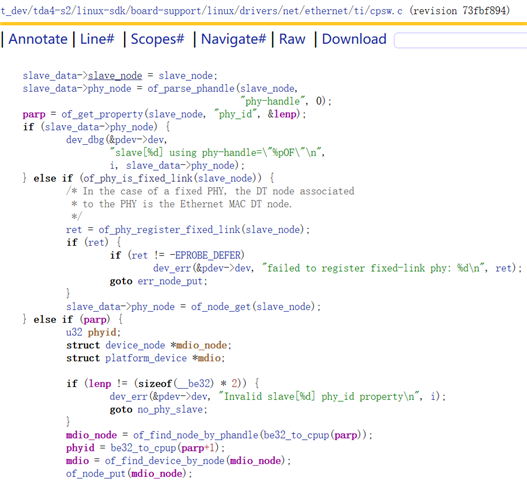

diff --git a/board-support/linux/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts b/board-support/linux/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts

index f0f475ea0..3ee13c666 100644

--- a/board-support/linux/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts

+++ b/board-support/linux/arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dts

@@ -609,20 +609,27 @@

&mcu_cpsw {

pinctrl-names = "default";

pinctrl-0 = <&mcu_cpsw_pins_default &mcu_mdio_pins_default>;

};

-&davinci_mdio {

- phy0: ethernet-phy@0 {

- reg = <0>;

- ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

- ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

- ti,min-output-impedance;

- };

-};

+//&davinci_mdio {

+// phy0: ethernet-phy@0 {

+// reg = <0>;

+// ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

+// ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

+// ti,min-output-impedance;

+// };

+//};

&cpsw_port1 {

phy-mode = "rgmii-rxid";

- phy-handle = <&phy0>;

+ fixed-link {

+ speed = <1000>;

+ full-duplex;

+ };

+// phy-handle = <&phy0>;

};

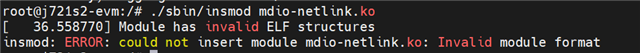

4.

Rtl9068 status:

GPIOA0~3 connected to the 9068 through the usbio adapter board has burned the 9068 firmware to the flash.

The 9068 uses the automatic startup scheme. The firmware driver is downloaded to the spi flash and starts by itself after being powered on. No need to write driver files.

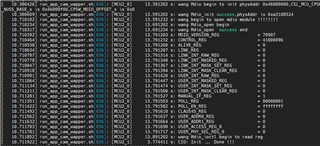

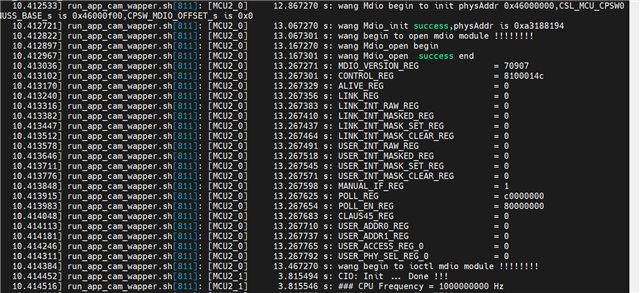

5. Test situation:

Now 9068 and tda4 are connected in MAC-to-Mac mode. It is connected to the mcu rgmii1 port of tda4. At present, the txc of 9068 and the txc of tda4 are both 125M clocks.

In addition, rgmii adopts the non-auto-negotiation mode. However, what we see through ethtool is auto-negotiation mode, and it is not clear how to change it. As shown below:

6.How to configure the rgmii port of the mcu on the linux side and set it to the non-auto-negotiation mode of mac to mac?