Hello,

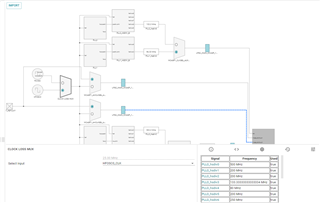

There is an audio function block called McASP in the AM62 series of devices.

According to user manuals and reference manuals, it seems that it is possible to set and use sample rates such as 48kHz and 44.1kHz with audio protocols such as I2S from McASP. Is it possible to set and use sample rates such as 8kHz and 16kHz at lower rates?

Best regards,

K.Hirano

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.