Other Parts Discussed in Thread: AM625

Hi,

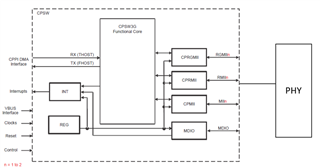

As per my understanding about the hardware connectivity of AM62x SKEVM PROC114E3, there are two hardware blocks available in this PCB as shown in the below figure. One is PHY and another is AM62x processor. In this AM62x processor, we have CPSW,ALE and CPPI blocks in hardware itself. Combination of all these blocks will be called as "CPSW_3G". Can you please confirm whether it is correct or not? And if it is wrong, then can you please provide me the exact connectivity?

Thanks & Regards,

Ch. Sai sirisha.