Other Parts Discussed in Thread: SYSCONFIG, TDA4VM, DRA829, J721EXSOMXEVM

Hi,

I am using SK-TDA4VM evl board (SDK: 08.06.01.02 (12 May 2023) PROCESSOR-SDK-LINUX-J721E).

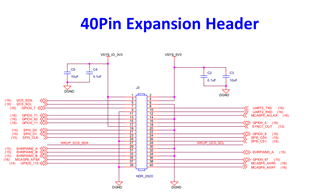

I want to use SPI interface available in 40-pin header. but do not see spidev under /dev/

I also referred https://e2e.ti.com/support/processors-group/processors/f/processors-forum/947437/faq-ccs-tda4vm-how-to-use-spi-spi_dev-on-tda4-j721e but could make spidev up I am sure I might have missed something.

Could you please share below details?

1) Which device tree files are for my board and how to enable SPI?

2) How to build and generate dtb and copy into board?

I have sdk code based on ti-processor-sdk-linux-j7-evm-08_06_01_02-Linux-x86-Install.bin

Thank you

Neeraj