Dear expert,

Could you please tell me the principle of PLL slip detector operation? How it can detect slip?

And is there any trim value/threshold for that to report a error? Thanks.

Best Regards,

Xingyu Zhu

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear expert,

Could you please tell me the principle of PLL slip detector operation? How it can detect slip?

And is there any trim value/threshold for that to report a error? Thanks.

Best Regards,

Xingyu Zhu

Hi Xingyu Zhu,

The Phase-Locked Loop (PLL) logic includes an embedded diagnostic that can detect a slip of the PLL output clock.

The slip is a result of a loss of phase lock between reference clock and feedback clock. Error response and indication is dependent on the programming of the PLL control registers that are located in the system module. The ESM module can be used for handling of error indication.

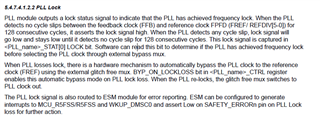

There is additional information in the TRM Section 5.4.7.4.1.2.2 PLL Lock.

Regards,

kb