Other Parts Discussed in Thread: AM625

Hello TI,

I am trying to load the u-boot spl from CCS and i referred below link

In above link had a broken link of compiling methods of u-boot from CCS, please provide the working link of compilation methods of u-boot from CCS.

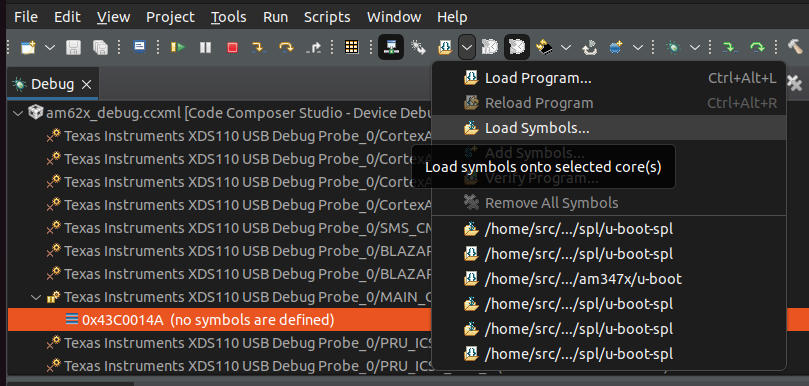

![]()

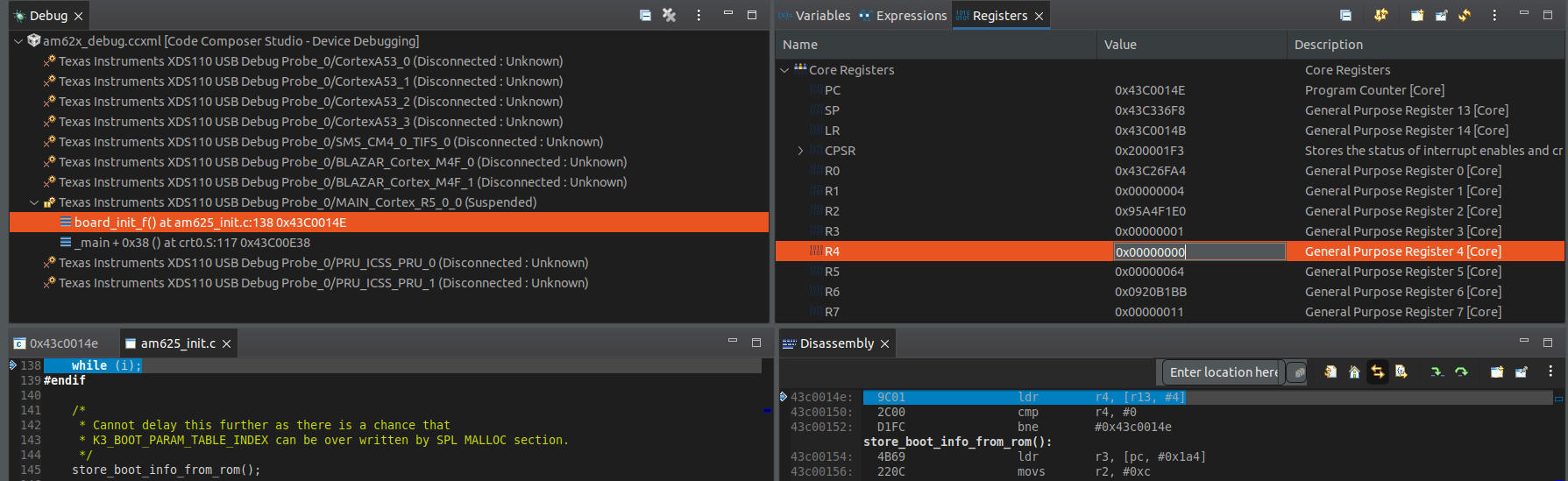

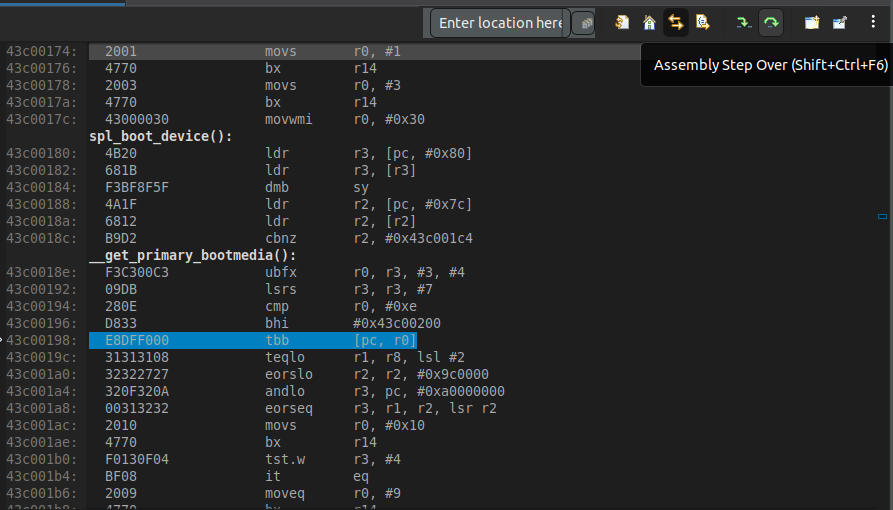

however i tried loading r5 spl by compiling outside of CCS, but not helping to debugging spl code.

additionally here few steps are not documented like how to load a53 spl and u-boot.img once r5 spl loaded. please provide document for it.

u-boot porting also i referred from resource explorer https://dev.ti.com/tirex/explore/node?node=A__ANjtmn.T3uPBiF9U2lCRWQ__linux_academy_am62x__XaWts8R__LATEST

but this page also not explained about loading spl from CCS.

we have to do our custom am62 board u-boot porting,

Please provide necessary document to debug the spl(r5, a53), u-boot.img from CCS.