Other Parts Discussed in Thread: TDA4VM, TDA4VH

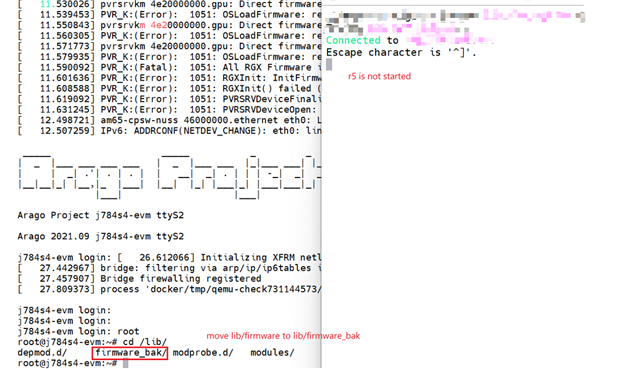

we are using the PROCESSOR-SDK-LINUX-J784S4-08.06.01 download from https://www.ti.com/tool/J784S4XEVM (Version: 08.06.01.02 Release date: 12 May 2023)

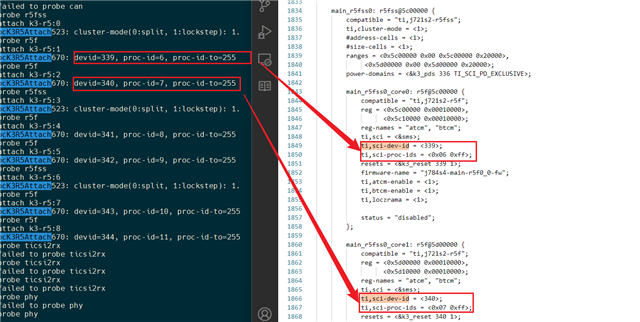

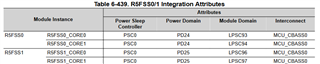

From the arch\arm64\boot\dts\ti\k3-j784s4-main.dtsi, we can see there are main_r5fss0/1/2 nodes for 6-R5 cores.

main_r5fss0: r5fss@5c00000 {

compatible = "ti,j721s2-r5fss";

ti,cluster-mode = <1>;

#address-cells = <1>;

#size-cells = <1>;

ranges = <0x5c00000 0x00 0x5c00000 0x20000>,

<0x5d00000 0x00 0x5d00000 0x20000>;

power-domains = <&k3_pds 336 TI_SCI_PD_EXCLUSIVE>;

main_r5fss0_core0: r5f@5c00000 {

compatible = "ti,j721s2-r5f";

reg = <0x5c00000 0x00010000>,

<0x5c10000 0x00010000>;

reg-names = "atcm", "btcm";

ti,sci = <&sms>;

ti,sci-dev-id = <339>;

ti,sci-proc-ids = <0x06 0xff>;

resets = <&k3_reset 339 1>;

firmware-name = "j784s4-main-r5f0_0-fw";

ti,atcm-enable = <1>;

ti,btcm-enable = <1>;

ti,loczrama = <1>;

status = "disabled";

};

main_r5fss0_core1: r5f@5d00000 {

compatible = "ti,j721s2-r5f";

reg = <0x5d00000 0x00010000>,

<0x5d10000 0x00010000>;

reg-names = "atcm", "btcm";

ti,sci = <&sms>;

ti,sci-dev-id = <340>;

ti,sci-proc-ids = <0x07 0xff>;

resets = <&k3_reset 340 1>;

firmware-name = "j784s4-main-r5f0_1-fw";

ti,atcm-enable = <1>;

ti,btcm-enable = <1>;

ti,loczrama = <1>;

status = "disabled";

};

};

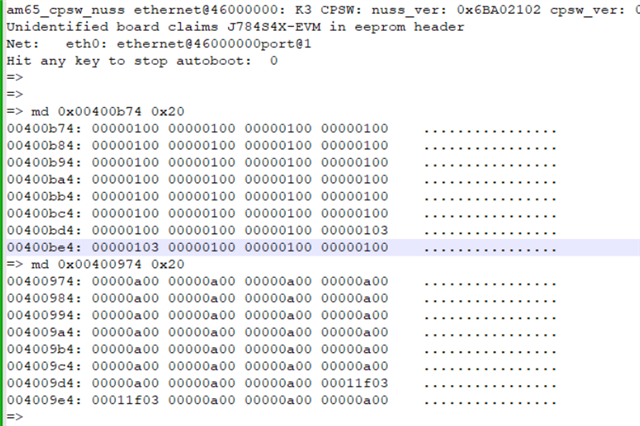

and we are porting the driver to initialize the R5F core, and met a problem (the linux version is OK),

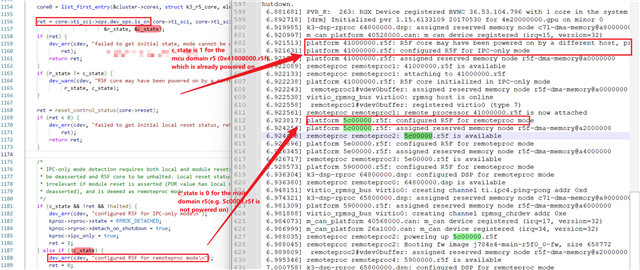

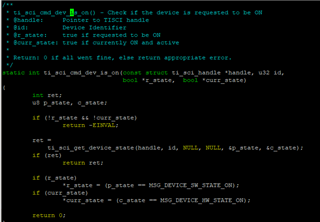

in our software flow, we use the SCI function to query the R5 status by the similar method on Linux:

//drivers\remoteproc\ti_k3_r5_remoteproc.c

static int k3_r5_rproc_configure_mode(struct k3_r5_rproc *kproc)

{

...

ret = core->ti_sci->ops.dev_ops.is_on(core->ti_sci, core->ti_sci_id,

&r_state, &c_state);

if (r_state != c_state) {

dev_warn(cdev, "R5F core may have been powered on by a different host, programmed state (%d) != actual state (%d)\n",

r_state, c_state);

}

...

}