Hi Champs,

Reference: TDA4VE datasheet page 124

Q1: Is the Delay between Reset and start of disable of first voltage required or can it be at the same time?

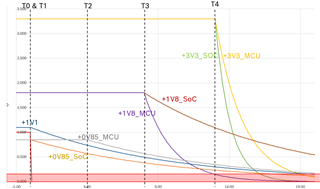

Q2: The datasheet specifies only discharge start times. Due to different amount of decoupling capacitors this may lead to the scenario that a later rail is discharged below 200mV before an earlier rail. Is this acceptable for the TDA4VE/L? Example: +1V8_MCU vs +0V85_MCU or +3V3_SOC vs +1V8_SOC in this picture.

Q3: Would the power-down in this picture satisfy the TDA4 requirements?

Q4: Would it be acceptable to start the discharge of +1V8_SOC already at T2 or even T1? Due to the higher voltage compared to +0V85, +1V1, ... it would always be higher, but the overall shutoff time could be reduced by several ms.

Kind regards, one and zero