Hi TI Experts,

Customer is using SDK8.6, and having their own CCS project based on SBL (no changes). They have already used their project to load and run all the cores successfully, except MCU1_1.

I have attached the linker files they applied below.

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/linker_5F00_r5f_5F00_freertos_5F00_common.inc

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/linker_5F00_r5f_5F00_mcu1_5F00_0_5F00_freertos.lds

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/linker_5F00_r5f_5F00_mcu1_5F00_1_5F00_freertos.lds

We have tried the below cases testing.

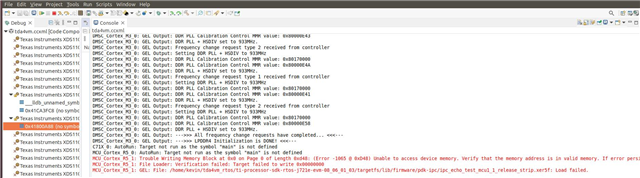

Case1: The .freertosrstvectors in MCU1_0 is using MCU_RF_TCMB_VECS, MCU1_1 is using MCU_R5F_TCMA_VECS. In this case MCU1_1 will have below errors when loaded to CCS.

MCU_Cortex_R5_1: Trouble Writing Memory Block at 0x0 on Page 0 of Length 0x2088: (Error -1065 @ 0x1000) Unable to access device memory. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.12.0.00150)

Case2: The .freertosrstvectors in MCU1_0 is using MCU_RF_TCMA_VECS, in MCU1_1 is using MCU_R5F_TCMA_VECS. In this case MCU1_1 will not have above errors, but it will not stop after being loaded to CCS. It can not enter the main function, when we stop the progress, it will have below errors.

No source available for "CSL_armR5StartupCacheInvalidateAllIcache + 0x8 () at Z

Case3: The .freertosrstvectors in MCU1_0 is using MCU_RF_TCMB_VECS, in MCU1_1 is using MCU_R5F_TCMB_VECS. In this case, it has the same problem as case2.

Could you help on this please?

Thanks a lot!

Kevin