Other Parts Discussed in Thread: TDA4VM

Hi TI experts,

I have some questions for DDR Register Configuration.

1.We use DDRSS Reg Config Tool 0.6.0 previously, which is updated to 0.10.0 version currently. Then I use the same input information and find there are differences for the generated codes. Could you clarify what points are updated. Are there some change notes?

2.Is it related to SDK version for DDRSS Reg Config Tool version. We use SDK7.3 and SDK8.5 for 2 varients of our projects and we use DDRSS Reg Config Tool 0.6.0 for both. Do you recommand updating it to 0.10.0 version?

3.We did encounter an issue about DDR. So I have to ask for your help. We find DDR stress failed on some test items sometimes, such as Bit spread and bit flip as the below log shows. Additionally, we use TI stress script and find no issues, while find issues with memtester tests. Is this because there are fewer test items in the TI script?

memtester stress test_306 cycles.txt

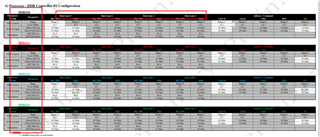

4.We just see this failure on 3 boards while we have built thousands of boards. Do you have any advice for this failure mode? Is there any related DDR Reg configuration we can optimize? For this reason, I attach our SCH, DDR Reg Configuration based 0.6.0 version for your review. We use micron DDR MT53E1G32D2FW-046 AUT:B, which is similar with EVM board.

0513.DDR SCH.pdfCopy of SPRACU8_Jacinto7_DDRSS_RegConfigTool--0711-4266.xlsm

Look forward to your suggestions. Thanks a lot!