Other Parts Discussed in Thread: TDA4VM

Hi,

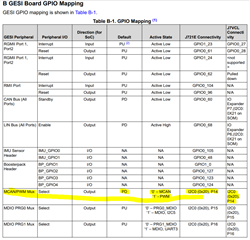

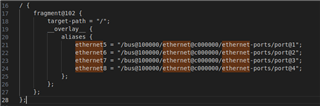

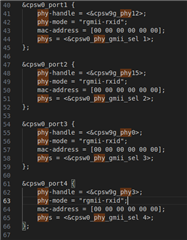

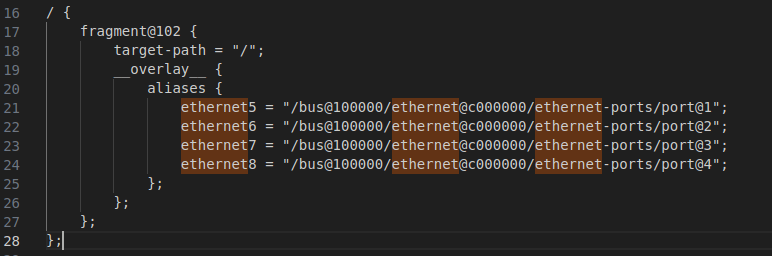

I am facing an issue in accessing all the ethernet ports and CAN channels on the Jacinto7 EVM Gateway/Ethernet Switch Expansion.

I have loaded the ethernet firmware manually and also vision apps.

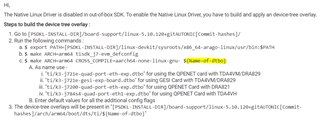

Following are the things that I have already tried. https://e2e.ti.com/support/processors-group/processors/f/processors-forum/929577/faq-tda4vm-how-to-get-cpsw9g-virtual-interface-functional-on-tda4x-dra8x-sdk-versions-7-0-onward

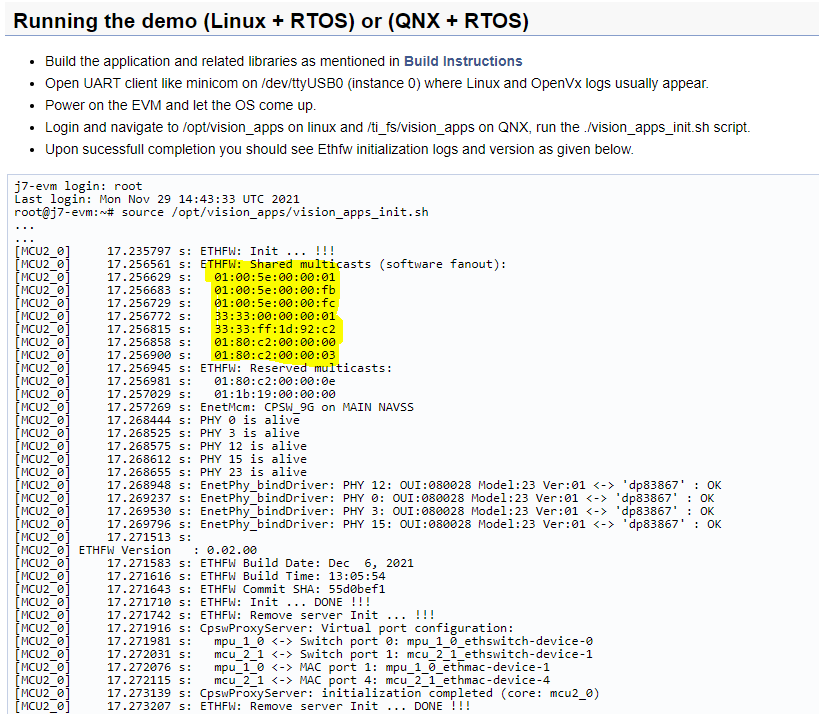

Vision apps installation: https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-jacinto7/08_06_01_03/exports/docs/vision_apps/docs/user_guide/RUN_INSTRUCTIONS.html.

On this website it is mentioned that there is no need to load ethfw manually. https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-jacinto7/08_06_01_03/exports/docs/vision_apps/docs/user_guide/ETHFW_DEMOS.html

Anyways I have still load ethfw manually by fallowing this software-dl.ti.com/.../ethfw_c_ug_top.html All the 8 ports are alive however, I can't see their MAC.

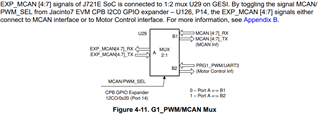

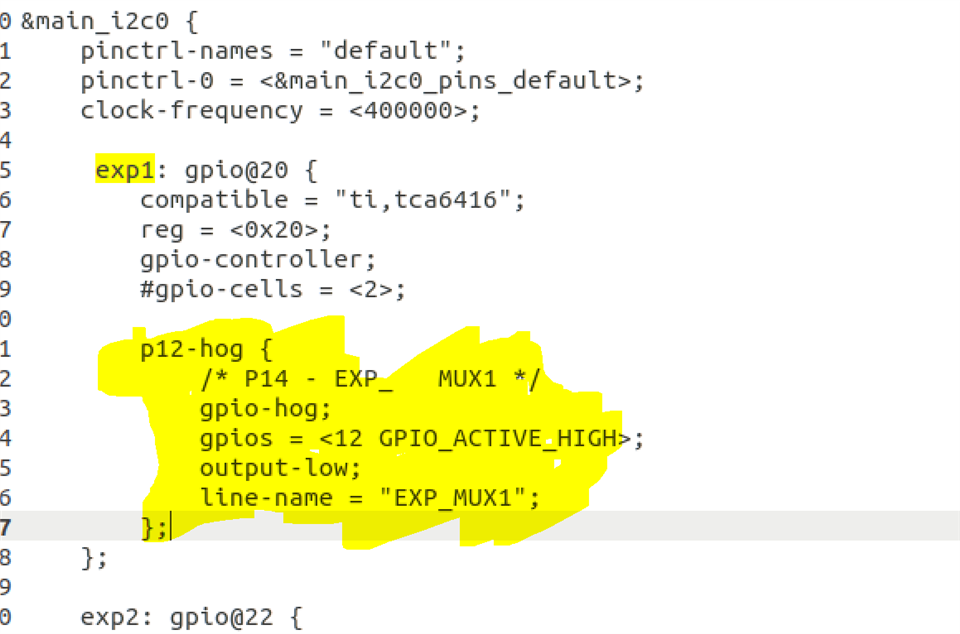

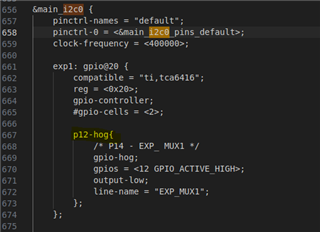

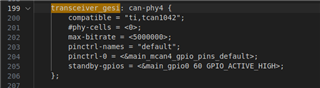

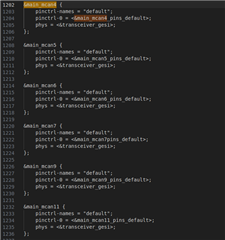

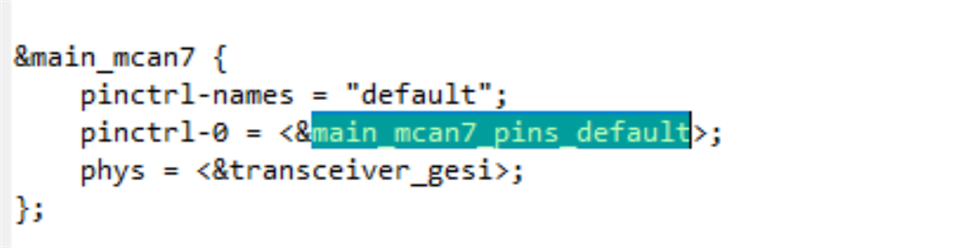

Moreover, I also want to enable all the CAN channels available on gateway.