Hi,

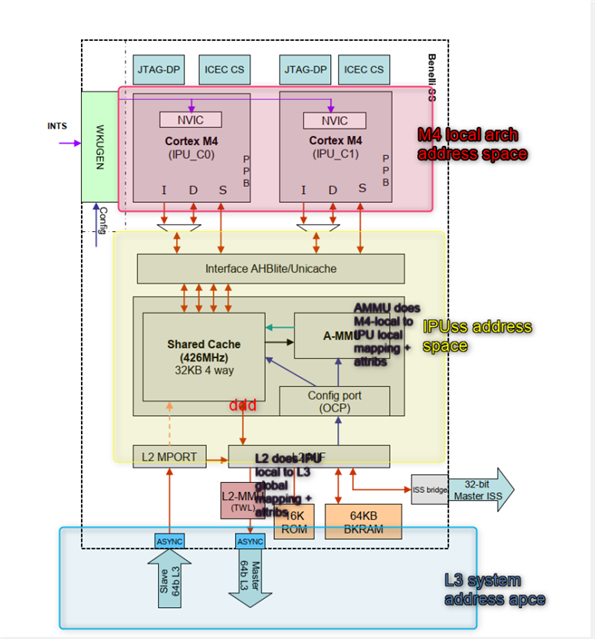

My customer has some questions about the specification of “AMMU-UNICACHE” of Dual Cortex-M4 IPU Subsystem on AM5706.

Q1) Could you tell them what “BYPASS-bit” of IPUx_UNICACHE_CFG Register means ?

The Register manual describes as “0x0: Everything is non-cacheable./0x1: Everything is cacheable.”. Does it mean that the IPU cache will not be enabled unless this bit is set ON ?

(Referring to the page 1748 in AM571x and AM570x TRM)

Q2) When “BYPASS-bit is set ON, memory access to the spaces other than those registered in AMMU is disabled.

They confirmed below.

- Accessing by program code => BusFault occurred

- Memory dump by ICE => Read impossible.

Is this operation the specification of this device ? If so, could you tell them any workaround ?

Also, they have confirmed that the area other than the AMMU registration space as well can be accessed when “BYPASS-bit” is set OFF.

< Information >

AM5706

CCS v8

TI v18.1.2.LTS

HW AM5706 Custom Board

SW pdk_am57xx_1_0_11

bios_6_76_00_08

XDCTools 3.50.3.33

ICE Lauterbach

Thanks and regards,

Hideaki