Other Parts Discussed in Thread: SYSCONFIG

The gpio_led_blink example in the sdk works fine for the red led on my LP-AM263.

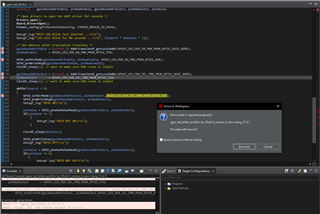

To test GPIO assignment I modified this basic example.

I connected an external led to pin 33 on booster pack header J4 and

used sysconfig to assign PRO_PRU0_GPIO0 to it which is

GPIO93 in standard multiplexing mode 7.

This modified blink program seems to work fine in processor memory, but the external led doesn't blink.

The external led works fine when it is powered by another 3.3V power supply.

But not here on pin 33 at booster pack header J4 with this program.

The multiplexing configuration made by sysconfig in ti_pinmux_config.c is:

static Pinmux_PerCfg_t gPinMuxMainDomainCfg[] = {

/* GPIO0 pin config */

/* GPIO26 -> UART0_CTSn (B7) */

{

PIN_UART0_CTSN,

( PIN_MODE(7) | PIN_PULL_DISABLE | PIN_SLEW_RATE_HIGH | PIN_QUAL_SYNC | PIN_GPIO_R5SS0_0 )

},

/* GPIO0 pin config */

/* GPIO93 -> PR0_PRU0_GPIO0 (K17) */

{

PIN_PR0_PRU0_GPIO0,

( PIN_MODE(7) | PIN_PULL_DISABLE | PIN_SLEW_RATE_HIGH | PIN_QUAL_SYNC | PIN_GPIO_R5SS0_0 )

},

/* GPIO0 pin config */

/* GPIO94 -> PR0_PRU0_GPIO1 (K18) */

{

PIN_PR0_PRU0_GPIO1,

( PIN_MODE(7) | PIN_PULL_DISABLE | PIN_SLEW_RATE_HIGH | PIN_QUAL_SYNC | PIN_GPIO_R5SS0_0 )

},

/* GPIO0 pin config */

/* GPIO96 -> PR0_PRU0_GPIO3 (J17) */

{

PIN_PR0_PRU0_GPIO3,

( PIN_MODE(7) | PIN_PULL_DISABLE | PIN_SLEW_RATE_HIGH | PIN_QUAL_SYNC | PIN_GPIO_R5SS0_0 )

},

/* UART0 pin config */

/* UART0_RXD -> UART0_RXD (A7) */

{

PIN_UART0_RXD,

( PIN_MODE(0) | PIN_PULL_DISABLE | PIN_SLEW_RATE_LOW )

},

/* UART0_TXD -> UART0_TXD (A6) */

{

PIN_UART0_TXD,

( PIN_MODE(0) | PIN_PULL_DISABLE | PIN_SLEW_RATE_LOW )

},

{PINMUX_END, PINMUX_END}

};

If processor pad K17 is connected to pin 33 at booster pack header J4 then this should work.

Why is this not working?

Help would be very much appreciated.

Kind regards

Robert