Hi Ti expert:

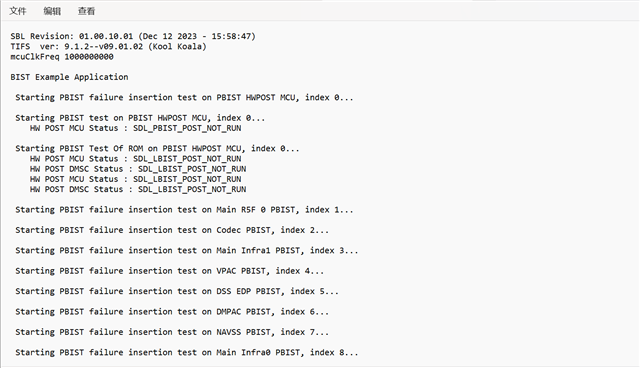

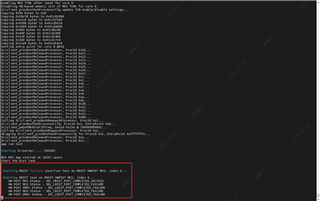

I implement SDL bist function from SDL example from the generated image.There has two images bist_example_r5f_baremetal_multicore_image.appimage and bist_example_r5f_baremetal_release.appimage.

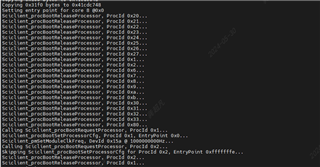

I get bist_example_r5f_baremetal_multicore_image.appimage include one MCU1_0 test app and C71 clearClecSerureCalim and another one MCU1_0 app doesn't work.From the uart boot log ,I can see C71 and MCU1_0 boot from SBL.

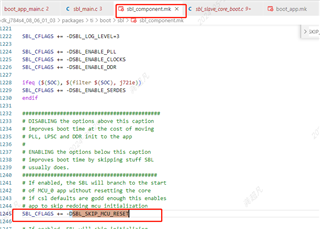

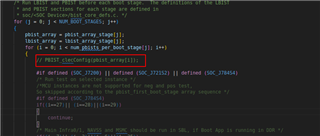

So the problems has happened,In the regular project the custom C71 code need to boot from MCU1_0 boot_app in the MCU1_0 app,I need implement bist function and boot custom C71.

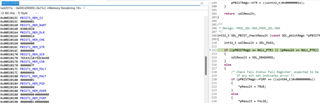

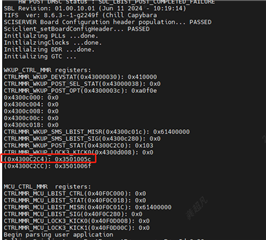

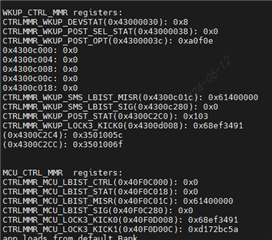

I try move clear secure code to custom C71 code,it seems work well,but when the PBIST and LBIST functions are done,try to boot A72 and Main R5 ,c71 are failed no any uart log.I use the XDS110 try to connect debug but failed.

Can you give me any suggestion or example can implement two function from the SDK? by the way the SDK9.0 /mcusw/mcuss_demos/boot_app_mcu_rtos can you show the selftest report?