Part Number: TMS320C6678

Hi Team,

When debugging the TSIP interface of the TMS320C6678 chip to V7 (FPGA), there're 2 issues:

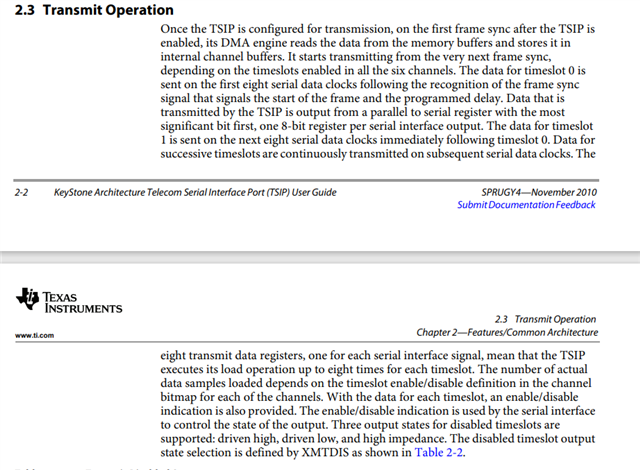

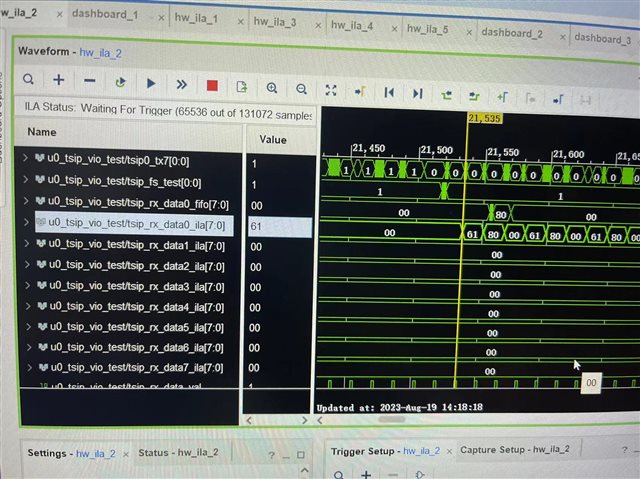

1) The TMS320C6678 data sent to the FPGA through the TSIP is not followed the rule as described in the manual: eight-bit data immediately followed by the eight-bit data, but 24b one data, as shown in the following figure:

The current data pattern is: 8B Data + 16b Idle Code. This problem severely affects the transmission bandwidth.

2) The data sent to the FPGA via the TSIP by the TMS320C6678 discards a portion of the data on the front edge (the packet length is not fixed), and the data on the rear edge is verified to be correct. The verification logic inside TI's official program does not care if the data on the front is lost, but this will affect the sending and receiving of commands when they are actually in use.

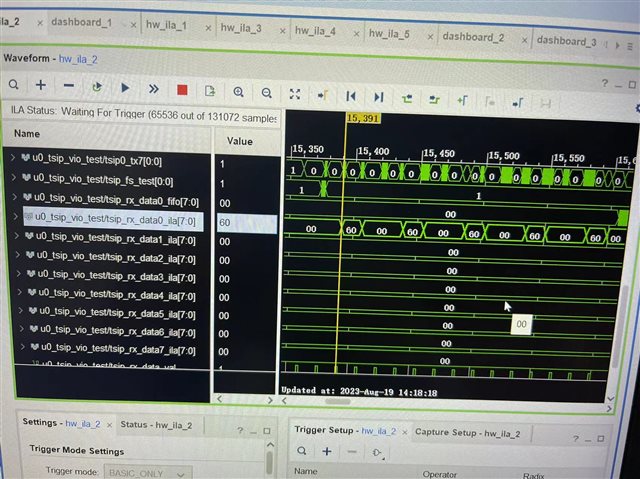

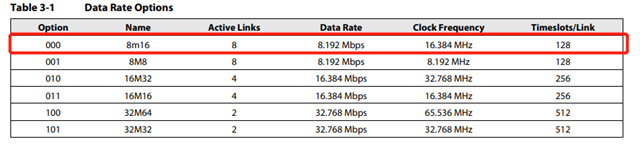

The TMS320C6678 driver currently in use is ccs930/PDK_c667x_2_0_16 with the following operating modes:

Could you please help check this case? Thanks.

Best Regards,

Cherry