Part Number: AM6442

Hello,

I am using AM6442 board, on a no-RTOS, bare-metal system on Windows.

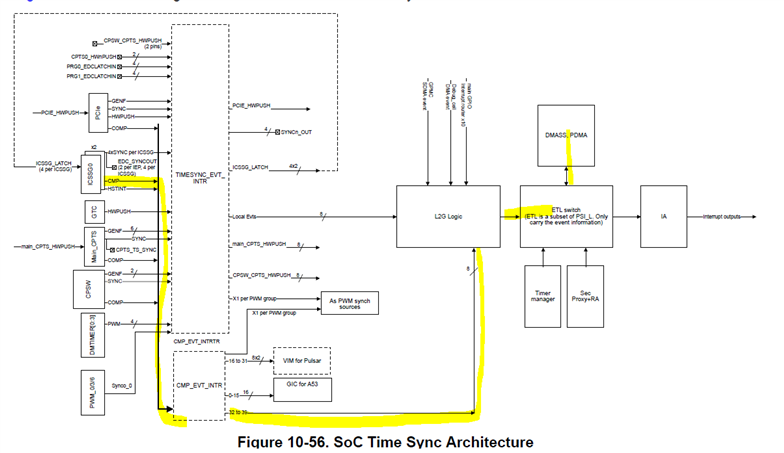

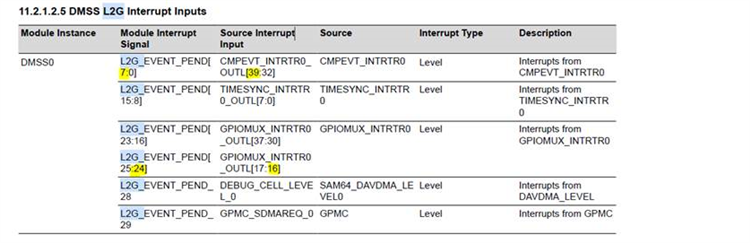

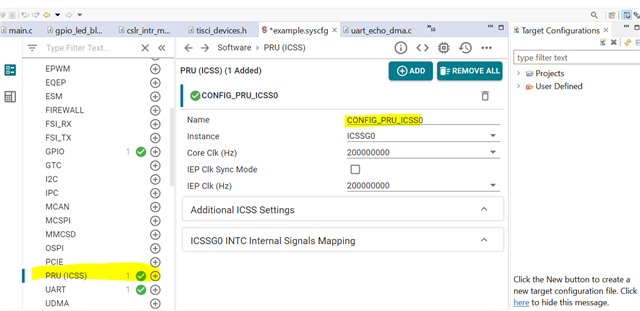

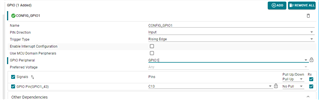

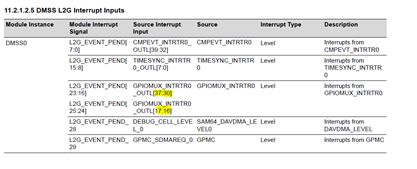

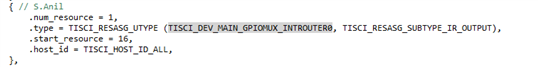

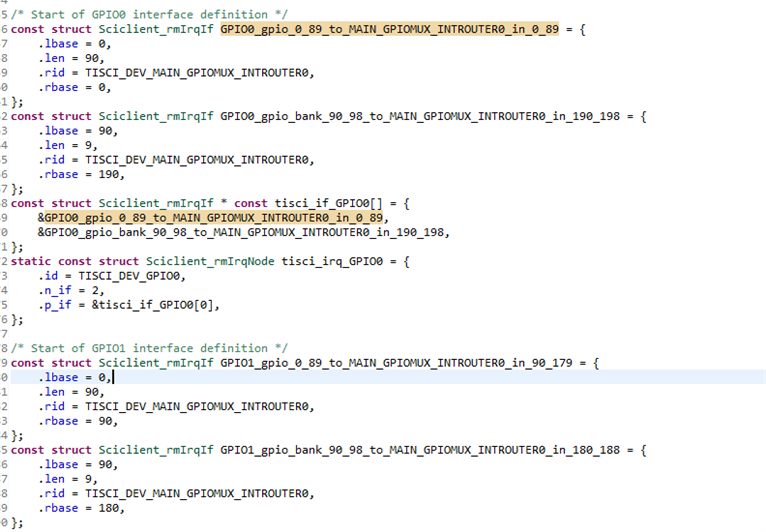

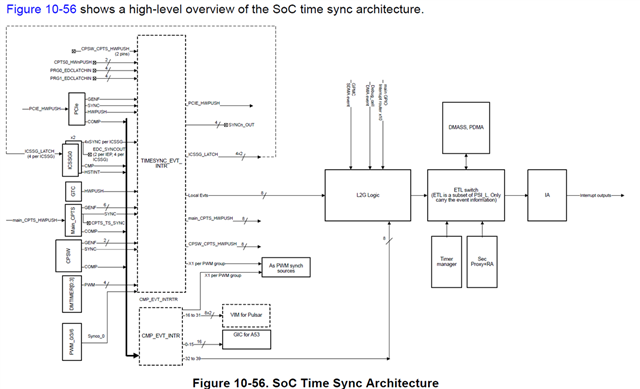

My final goal is to use GPMC to connect to an external FPGA and use the UDMA for transfers. So far I was able to read from GPMC with DMA while a software event triggers the start of transfer for BCDMA. Now I would like to define a timer to trigger the BCDMA transfer each 700us. I believe I should use the CMP_EVT_INT. But I don't know how should I do it. Can you give me a little detail about how I should do it? I would appreciate it if you could give me an example of how to use and define this CMP_EVT_INT and how to route it to trigger my BCDMA?

Thanks,

Boshra