Other Parts Discussed in Thread: TDA4VH

Hi TI Clock Experts,

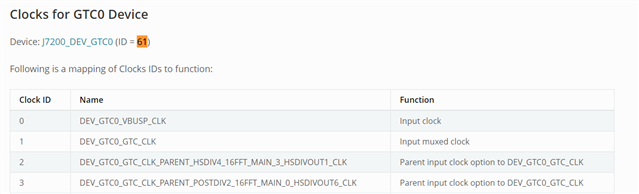

Customer is trying to design some synchronization tasks between different cores based on TDA4VH SDK8.6.

As we know, apart from GTC, we also have Linux system clock like CLOCK_MONOTONIC.

The question is that do we have any other Linux system clock which is also related to GTC?

Thanks a lot,

Kevin