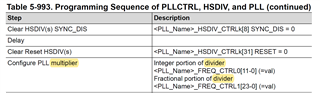

In the AM64x TRM PLL registers, is it wrong? it should be multiplier in FREQ_CTRL0?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

In the AM64x TRM PLL registers, is it wrong? it should be multiplier in FREQ_CTRL0?

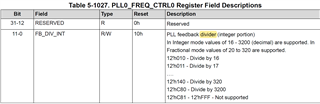

A PLL adjusts it output frequency to be a multiple of the reference clock frequency by providing a feedback path with clock dividers and a comparator that increases or decreases the PLL oscillator frequency until the divided feedback path matches the reference clock frequency. The dividers inserted into the feedback path are used to configure the PLL multiplier.

You configure a divider in the feedback path to set the PLL multiplier. Therefore, the description is correct.

Regards,

Paul