Other Parts Discussed in Thread: AM6442

Hello,

We’re reaching you out in order to get support on a recently issue we’re facing.

Currently we do have setup composed by a J784s4 (J784S4XG01EVM) as Root Complex connected through PCIe to AM64x (TMDS64EVM) as End Point.

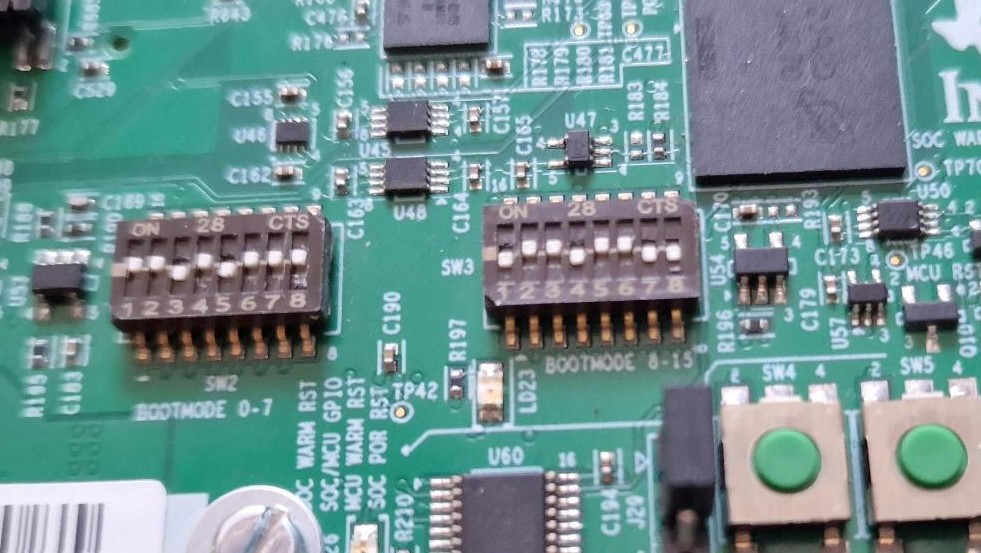

What we would like to achieve is boot TMDS64EVM through PCIe via J784s4. And for that we changed the TMDS64EVM DIP switches accordingly:

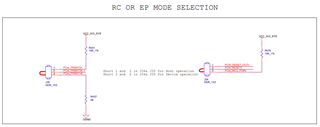

Additionally we do also select TMDS64EVM as an endpoint through jumper J34 and J35,

and R667/R668 where removed to avoid refclk contention on PCIe connector ,

Then we perform the following:

- 1st Sitara is powered on

- 2nd Jacinto is powered on -> Logging starts running, after about 17 seconds PCIe reset, coming from Jacinto over the PCIe cable, is de-asserted

- After Jacinto is booted the “lspci” command is executed. Only the PCIe devices on the Jacinto board are seen.

- No Sitara endpoints are seen on the PCIe bus

- Tried several boot cycles without success.

- SerDesClk on Sitara starts running after about 17 seconds -> Seems to relate to PCIe reset de-assertion

- Changed cables and PCIe connector 0 to 1 on Jacinto, but without success.

- Powered on Jacinto first and after a few seconds Sitara, but without success.

Basically what we do expect is to see the Sitara EP on Jacinto and eventually access to the proper BAR to boot Sitara. So,

- Are those expectations corrects?

- And if correct what could be wrong with this setup?

Let me know if you need more information.

Kind Regards,

Paulo Machado