Other Parts Discussed in Thread: AMIC110, CC2650MODA

Hi Expert,

We have two inquiries regarding AM3352.

・About interrupts

The following statement was found in P4983 of the AM335x and AMIC110 Sitara Processors Technical Reference Manual.

Due to the sampling operation, the minimum pulse width on the input GPIO to trigger a synchronous interrupt request is two times the internally gated interface clock period (the internally gated interface clock period is equal to N times the interface clock period).

This minimum pulse width has to be met before and after any expected level transition detection. Level detection requires the selected level to be stable for at least two times the internally gated interface clock period to trigger a synchronous interrupt.

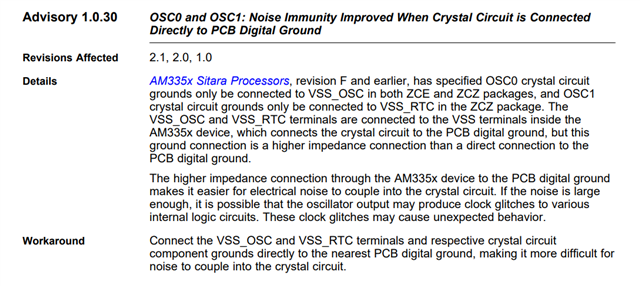

Can the interface clock be considered equivalent to the clock frequency input to OSC0_IN?

・About the internal clock

Is there a block that internally multiplies the clock from OSC0_IN?

In EMC, there are many spectrums that are multiplied by 25MHz input from OSC0_IN, and I am looking for any part of the multiplication within AM3352.

Best regards,

R.Sakai