Other Parts Discussed in Thread: SK-AM64B

CCS:12.3.0

SDK: mcu_plus_sdk_am64x_08_06_00_45\examples\networking\enet_layer2_multi_channel

EVM:SK-AM64B

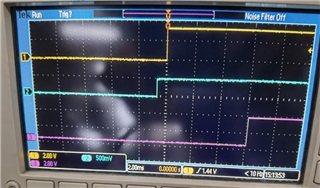

I want to generate PPS synchronized to the network Clock(PTP/IEEE 1588), and then Data acquisition sync to PPS. I have got PPS from two SK board, but the two PPS are asynchronized.

As shown above, the yellow one is PPS from SK board, the middle green PPS is from Clock Switch, they are synchronized at the beginning, but the green one moved to left slowly, they asynchronized.

I generated PPS by CPSW/CPTS GENF0 with GENF0 PPM disabled.

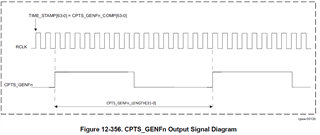

As shown below, when TIME_STAMP[63-0] = CPTS_GENFn_COMP[63-0] PPS is generated, thereafter the CPTS_GENFn_LENGTH[31-0] is independ of TIME_STAMP[63-0].

CPTS_GENFn_LENGTH counted the CPTS_REF_CLK, that is to say, the period which depended on CPTS_REF_CLK is stationary.

Am I correct about the figure in TRM?

But it seems the counter of CPTS_REF_CLK is unstable, it seems to be adjusted by the TIME-STAMP[63-0],because CPTS_GENFn_LENGTH[31-0] is static after init.

Please check my use of CPTS GENF.

Waiting for your reply.

Thans you very much.