Part Number: TMDS64GPEVM

Hi TI Experts

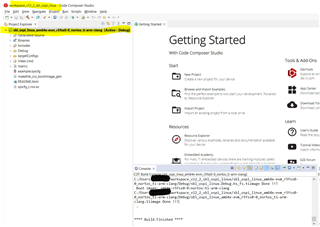

I am working on an ethernet-sbl project on mcu_plus_sdk_08_05_00_24 sdk version. Also my CCS version is 12.1.

When I build my project in Debug mode, I get an this error.

"../linker.cmd", line 16: error #10099-D: program will not fit into available memory, or the section contains a call site that requires a trampoline that can't be generated for this section. run placement with alignment fails for section "GROUP_1" size 0x80e3e. Available memory ranges: MSRAM0 size: 0x7ff00 unused: 0x7ff00 max hole: 0x7ff00

But when I build the project in Release mode, I didn't encounter any problem like this.

This is my linker.cmd file

#include "ti_enet_config.h"

--stack_size=16384

--heap_size=32768

-e_vectors_sbl /* for SBL make sure to set entry point to _vectors_sbl */

__IRQ_STACK_SIZE = 4096;

__FIQ_STACK_SIZE = 256;

__SVC_STACK_SIZE = 256;

__ABORT_STACK_SIZE = 256;

__UNDEFINED_STACK_SIZE = 256;

SECTIONS

{

.vectors:{} palign(8) > MSRAM_VECS

GROUP {

.text: {} palign(8)

.text.hwi: palign(8)

.text.cache: palign(8)

.text.mpu: palign(8)

.text.boot: palign(8)

.data: {} palign(8)

.rodata: {} palign(8)

} > MSRAM0

GROUP {

.sysmem: {} palign(8)

.stack: {} palign(8)

} > MSRAM1

GROUP {

.sysmem: {} palign(8)

.stack: {} palign(8)

} > MSRAM1

.bss: {} palign(8) > MSRAM1

RUN_START(__BSS_START)

RUN_END(__BSS_END)

GROUP {

.irqstack: {. = . + __IRQ_STACK_SIZE;} align(8)

RUN_START(__IRQ_STACK_START)

RUN_END(__IRQ_STACK_END)

.fiqstack: {. = . + __FIQ_STACK_SIZE;} align(8)

RUN_START(__FIQ_STACK_START)

RUN_END(__FIQ_STACK_END)

.svcstack: {. = . + __SVC_STACK_SIZE;} align(8)

RUN_START(__SVC_STACK_START)

RUN_END(__SVC_STACK_END)

.abortstack: {. = . + __ABORT_STACK_SIZE;} align(8)

RUN_START(__ABORT_STACK_START)

RUN_END(__ABORT_STACK_END)

.undefinedstack: {. = . + __UNDEFINED_STACK_SIZE;} align(8)

RUN_START(__UNDEFINED_STACK_START)

RUN_END(__UNDEFINED_STACK_END)

} > MSRAM_1

/* General purpose user shared memory, used in some examples */

.bss.user_shared_mem (NOLOAD) : {} > USER_SHM_MEM

/* this is used when Debug log's to shared memory are enabled, else this is not used */

.bss.log_shared_mem (NOLOAD) : {} > LOG_SHM_MEM

/* this is used only when IPC RPMessage is enabled, else this is not used */

.bss.ipc_vring_mem (NOLOAD) : {} > RTOS_NORTOS_IPC_SHM_MEM

.enet_dma_mem {

*(*ENET_DMA_DESC_MEMPOOL)

*(*ENET_DMA_RING_MEMPOOL)

#if (ENET_SYSCFG_PKT_POOL_ENABLE == 1)

*(*ENET_DMA_PKT_MEMPOOL)

#endif

} (NOLOAD) {} ALIGN (128) > DDR

.bss:ENET_DMA_OBJ_MEM (NOLOAD) {} ALIGN (128) > MSRAM1

.bss:ENET_DMA_PKT_INFO_MEMPOOL (NOLOAD) {} ALIGN (128) > MSRAM1

.bss:ENET_ICSSG_OCMC_MEM (NOLOAD) {} ALIGN (128) > MSRAM1

}

/*

NOTE: Below memory is reserved for DMSC usage

- During Boot till security handoff is complete

0x701E0000 - 0x701FFFFF (128KB)

- After "Security Handoff" is complete (i.e at run time)

0x701FC000 - 0x701FFFFF (16KB)

Security handoff is complete when this message is sent to the DMSC,

TISCI_MSG_SEC_HANDOVER

This should be sent once all cores are loaded and all application

specific firewall calls are setup.

*/

MEMORY

{

R5F_VECS : ORIGIN = 0x00000000 , LENGTH = 0x00000040

R5F_TCMA : ORIGIN = 0x00000040 , LENGTH = 0x00007FC0

R5F_TCMB0 : ORIGIN = 0x41010000 , LENGTH = 0x00008000

MSRAM_VECS: ORIGIN = 0x70000000 , LENGTH = 0x100

/* when using multi-core application's i.e more than one R5F/M4F active, make sure

* this memory does not overlap with other R5F's

*/

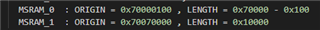

MSRAM0 : ORIGIN = 0x70000100 , LENGTH = 0x8000-0x100

MSRAM1 : ORIGIN = 0x70080000 , LENGTH = 0x4000

/* This section can be used to put XIP section of the application in flash, make sure this does not overlap with

* other CPUs. Also make sure to add a MPU entry for this section and mark it as cached and code executable

*/

FLASH : ORIGIN = 0x60200000 , LENGTH = 0x100000

/* when using multi-core application's i.e more than one R5F/M4F active, make sure

* this memory does not overlap with other R5F's

*/

DDR : ORIGIN = 0x80000000 , LENGTH = 0x1F0000

/* shared memory segments */

/* On R5F,

* - make sure there is a MPU entry which maps below regions as non-cache

*/

USER_SHM_MEM : ORIGIN = 0x701D0000, LENGTH = 0x00004000

LOG_SHM_MEM : ORIGIN = 0x701D4000, LENGTH = 0x00004000

RTOS_NORTOS_IPC_SHM_MEM : ORIGIN = 0x701D8000, LENGTH = 0x00008000

}

What is the reason of this problem? How can I solve?

Thanks...