Hi TI Expert,

Customer is working on SDK8.6. They have done the following 4 mailbox communication tests.

(1) r5 -> r5, the latency is 2.4us

(2) a72 -> r5, the latency is 0.9us

(3) r5 -> a72, the latency is 5ms

(4) a72 mailbox loop test, the latency is 5ms

Based on the test results, the test 3 & 4 is not normal, as our benchmark is provided in the below link section 1.1.2.6 .

The detailed setup of test 4 is described below.

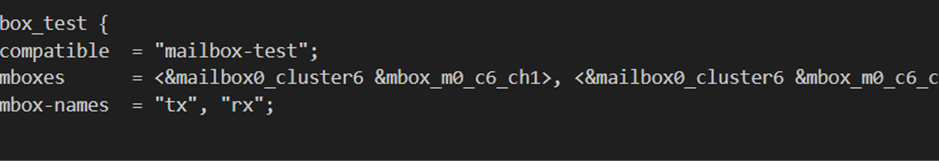

The file used is: driver/mailbox/mailbox-test.c

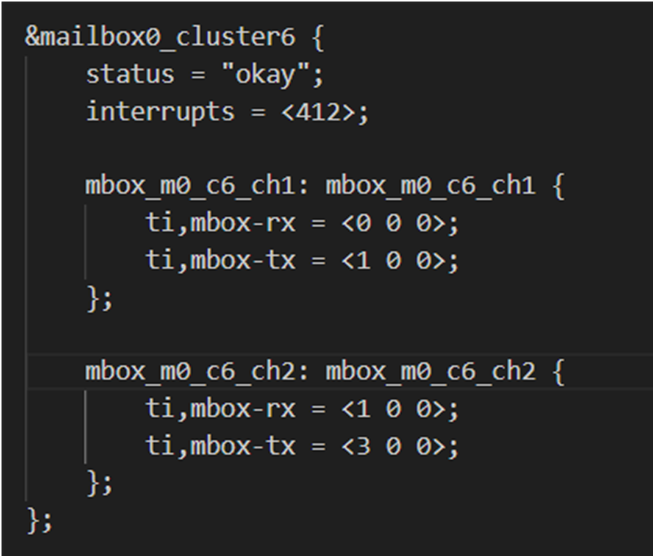

Both of the Tx & Rx use FiFo_1 in mailbox0_cluster6 shown below.

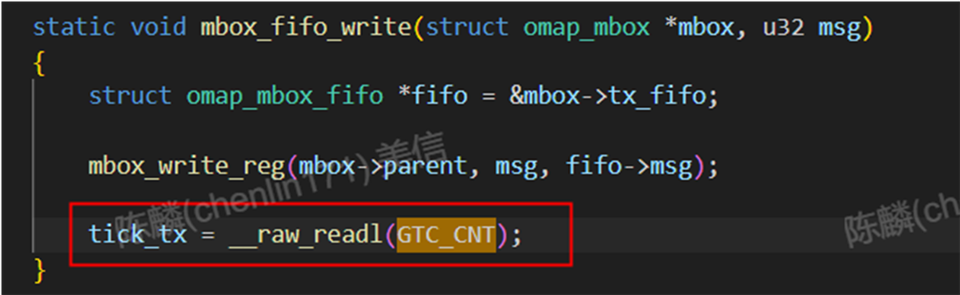

After the driver/mailbox/omap-mailbox.c sends out the tx, customer used below coding to record the GTC_CNT.

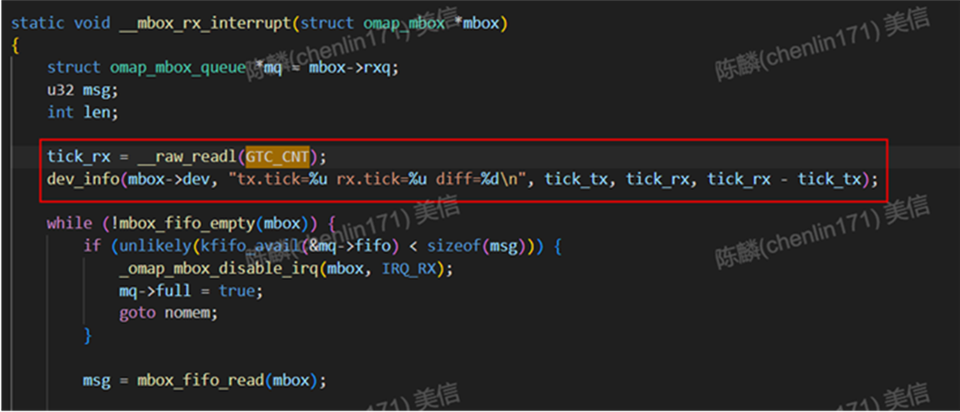

Then in the rx interrupt, using the below code to record the GTC_CNT again, & print out the latency.

As we know the 5ms performance result is not normal, may I know what could be the reasons for this test case. Could you provide some suggestions please?

Thanks a lot!

Kevin