Hi,.

We have a question from one of our customers.

They are using AM437x and are running Linux with SDK 7.3.1

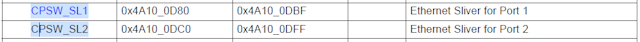

They are using two channels of Ethernet, but when they look at the process to set the spped settings for LAN, they see that in _cpsw_adjust_link() in the CPSW driver (drivers/net/ethernet/ti/cpsw.c), only the CPSW_SL_MACCTRL register, only IFCTL_A appears to be set.

static void _cpsw_adjust_link(struct cpsw_slave *slave,

struct cpsw_priv *priv, bool *link)

{

struct phy_device *phy = slave->phy;

u32 mac_control = 0;

:

/* set speed_in input in case RMII mode is used in 100Mbps */

if (phy->speed == 100) ★

mac_control |= CPSW_SL_CTL_IFCTL_A; ★

:

If they refer to the Technical Reference Manual, the IFCTL_B, IFCLT_A registers are defined and the IFCTL_B setting process appears to be missing.

Operationally, both CHs operate at 100 Mbps, but they believe that the IFCTL_B setting may need to be added to the driver.

Best Regards,

Kouji Nishigata