Hi,TI expert:

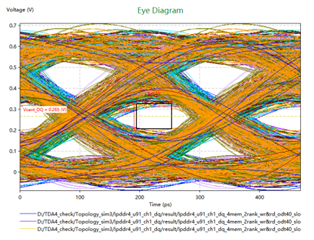

We simulated LPDDR4 in IBIS model's slow mode, but failed at 4266 data rate(as it show as below), could you help review our board file cut in sigrity and give us some advice (please contact xingyu-zhu@ti.com to get .spd file) ?

Also we would liketo know, have you tried to simulate LPDDR4 signals in slow mode in the file "Jacinto 7 LPDDR4 Board Design and Layout Guidelines"?

Looking foward to your reply as soon as possible. This question delay our gerber out time