Other Parts Discussed in Thread: TDA4VH

Hello all,

While reading the manuals, I found some confusing information that I need to clarify:

Here, 9.2. Understanding bootloaders in Processor SDK J784S4 (RTOS/Linux) — Processor SDK RTOS J784S4 (ti.com)

We can see it says that the RTOS binaries are copied using the below rule:

"

/lib/firmware/j784s4-<cpu>-fw

"

In section 9.3. MCU1_0 Application Development with SYSFW — Processor SDK RTOS J784S4,

( 9.3. MCU1_0 Application Development with SYSFW — Processor SDK RTOS J784S4)

We have this:

"

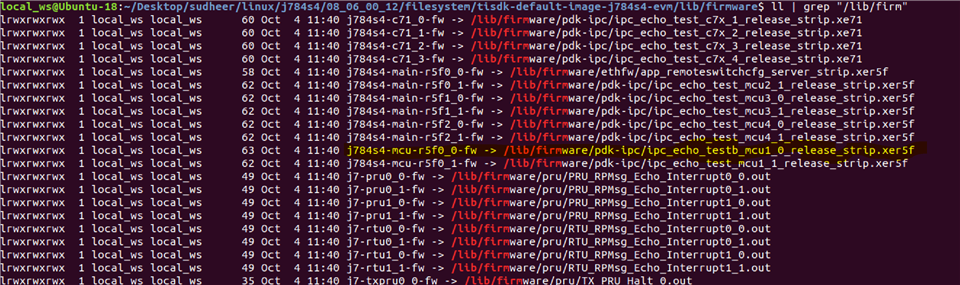

By default, the file system that comes in the Processor SDK Linux package has simple echo test firmware built using the RTOS PDK for each RTOS core as shown below. The highlighted line corresponds to the MCU1_0 firmware which already includes the SCISERVER and RM/PM services.

j7-c66_0-fw -> pdk-ipc/ipc_echo_test_c66xdsp_1_release_strip.xe66

j7-c66_1-fw -> pdk-ipc/ipc_echo_test_c66xdsp_2_release_strip.xe66

j7-c71_0-fw -> pdk-ipc/ipc_echo_test_c7x_1_release_strip.xe71

j7-c71_1-fw -> pdk-ipc/ipc_echo_test_c7x_2_release_strip.xe71

j7-main-r5f0_0-fw -> ethfw/app_remoteswitchcfg_server_strip.xer5f

j7-main-r5f0_1-fw -> pdk-ipc/ipc_echo_test_mcu2_1_release_strip.xer5f

j7-main-r5f1_0-fw -> pdk-ipc/ipc_echo_test_mcu3_0_release_strip.xer5f

j7-main-r5f1_1-fw -> pdk-ipc/ipc_echo_test_mcu3_1_release_strip.xer5f

j7-mcu-r5f0_0-fw -> pdk-ipc/ipc_echo_testb_mcu1_0_release_strip.xer5f

j7-mcu-r5f0_1-fw -> pdk-ipc/ipc_echo_test_mcu1_1_release_strip.xer5f

"

Highlighted is:

"j7-main-r5f1_1-fw -> pdk-ipc/ipc_echo_test_mcu3_1_release_strip.xer5f"

As you can see, this shows a different naming convention.

Also, I understood from other bits and pieces of documentation that the MCU domain is the safety island, where MCU1_0 and MCU1_1 reside, and in the highlighted one, we can see that the soft link points to "ipc_echo_test_mcu3_1_release_strip.xer5f", which I think was built for mcu3_1...??

By the way, in the make command, it shows a different file:

btw, in the make command, it shows a different file:

"

$(MAKE) -C $(PSDK_LINUX_PATH)/board-support/u-boot-* ARCH=arm CROSS_COMPILE=$(GCC_LINUX_ARM_ROOT)/bin/aarch64-none-linux-gnu- \ ATF=$(PSDK_LINUX_PATH)/board-support/prebuilt-images/bl31.bin \ TEE=$(PSDK_LINUX_PATH)/board-support/prebuilt-images/bl32.bin \ DM=$(FIRMWARE_PATH)/ipc_echo_testb_mcu1_0_release_strip.xer5f \ O=j721e-arm64-linux

"

Also, why does the firmware name contain the word "main"?

Can someone please help me understand what naming convention I should use to have the software I build using the RTOS PDK run on the desired core? (And be sure about it?)

Br, Mircea