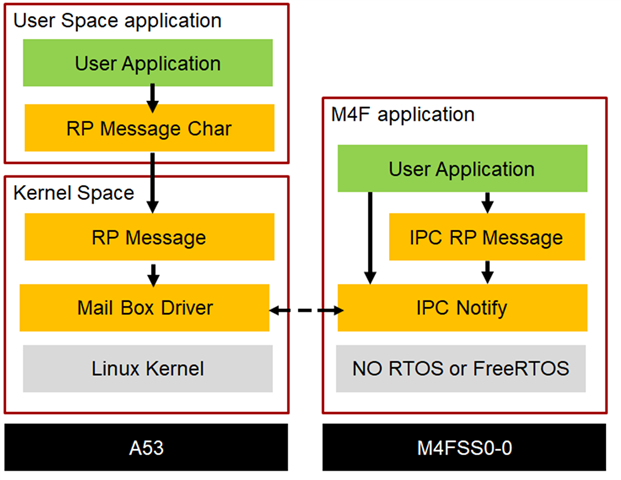

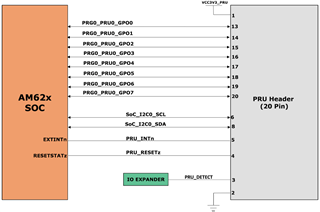

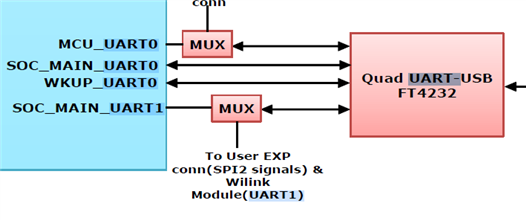

Verification for A53 and M4 / R5 Hybrid Communication Verification

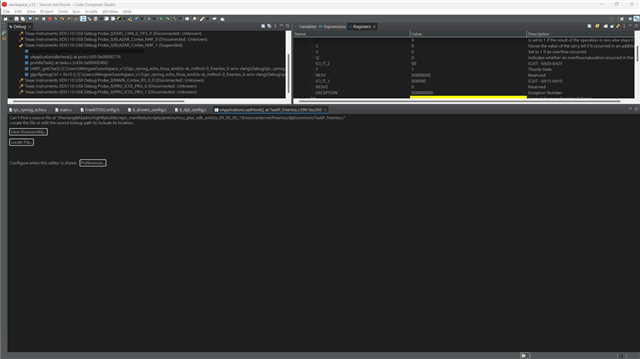

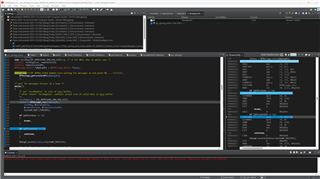

1. Development environment with CCS has already been established.

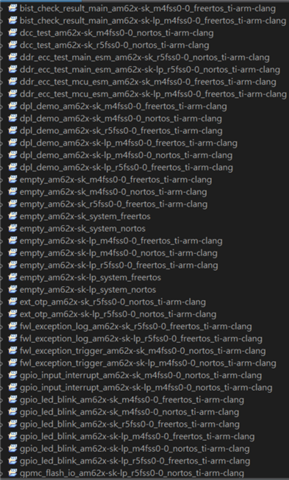

2. Reading RTOS/NO-RTOS [MCU+ SDK] documentation.

M4/R5 seems somewhat similar yet different. Are there more formal documentation or information available to understand the differences or usage scenarios?

It seems the same from the CCS samples.

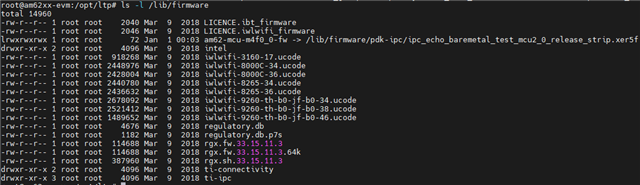

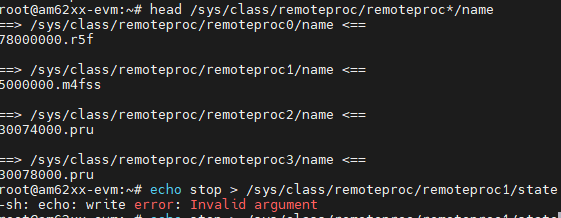

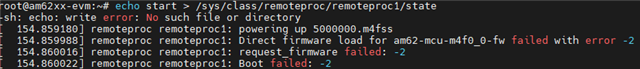

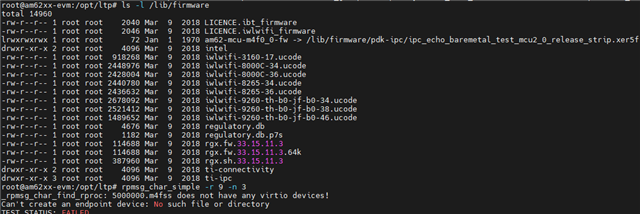

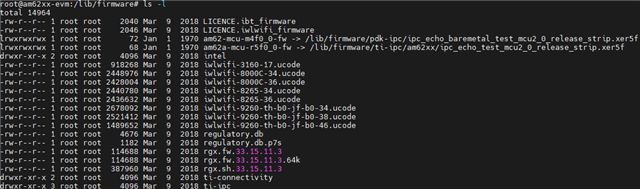

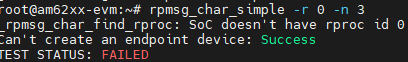

3. Does A53 require loading a specific DTS file (Processor SDK Linux for AM62x09_00_00_03)? Or is there a need for any modifications?

RTOS/NO-RTOS [MCU+ SDK] seems to focus more on the MCU, and it appears that Processor SDK Linux for AM62x doesn't provide much explanation in this regard.