Other Parts Discussed in Thread: TDA4VL

Hi,experts

Please help analyze a system exception and how to solve it.

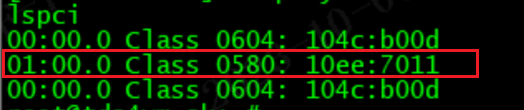

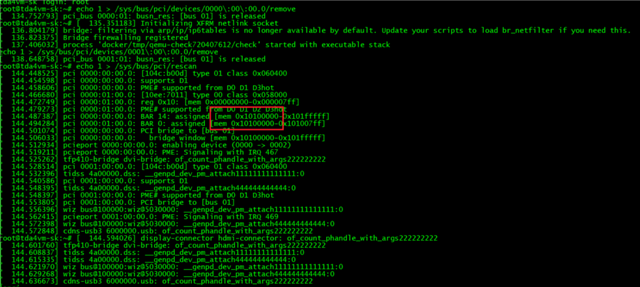

We have a board that uses TDA4VM as PCIE RC and FPGA as EP, and uses echo 1 > /sys/bus/pci/rescan to detect ep devices.

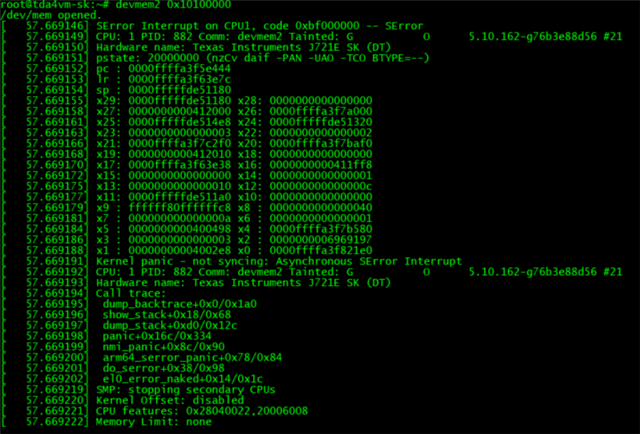

And access the BAR address through devmem2, but a system exception occurred.

Thank you.