Other Parts Discussed in Thread: SYSCONFIG

I changed the DDR access priority using "Class of Service (CoS)" of DDRSS and confirmed the operation of DDR access.

However, the results were not as expected.

What I confirmed are the following (a) and (b).

(a):

Leave the "Class of Service" as default (all with the same priority), continue to write 4 Bytes to DDR with the R5F core, and obtain the time it takes for the A53 core to read 4 Bytes to DDR while R5F is writing.

If you increase the number of R5F cores that perform 4Byte Writes to DDR, the time it takes for A53 cores to read 4Bytes to DDR will also increase.

This is the expected result.

(b):

In "Class of Service", change the priority of the A53 core to high and the other priorities to low, and check the same as in (a).

Since I changed the DDR access priority of the A53 core to high, I thought that the time required for reading the A53 core would be shorter than in (a), but the result is the same as in (a).

Please let me know about my next question.

Q1:

Why is the result in (b) the same as in (a)?

Q2:

Am I using DDRSS's "Class of Service (CoS)" incorrectly?

I have attached the project used for confirmation.

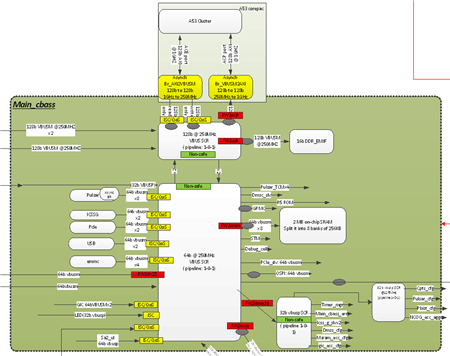

For information on configuring Class of Service, refer to the next chapter of TRM.

AM64x/AM243x Technical Reference Manual (Rev. G)

3.3.1 Route ID

8.1.4.1 Class of Service (CoS)

I'm using the following environment:

AM64x EVM TMDS64GPEVM (SR1.0)

AM64x MCU+ SDK (Ver.08.03.00)

Example:Empty Project

Code Composer Studio (Ver.12.4.0)

SysConfig Tool (Ver.1.12.1)