Other Parts Discussed in Thread: DRA829

Hello TI,

I am experimenting with FreeRTOS awarness in T32 and I notice that any "Display of kernel resources" for FreeRTOS (task list, semaphores, timers, etc) are not updated on the fly, but only after stopping CPU execution.

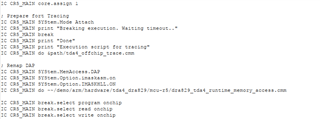

For that use case I configure DAP and remap TCM just using script provided to configure properly ("dra829_tda4_runtime_memory_access", by Richard Woodruff)

In order to not have issues with SMP restriction,

I assign just one core to slave instance:

Could it be any problem with addresses of remapped in script? Could you point to documentation to understand better allocation of TCMA/B, the remapped areas and other stuff to be clever in the understanding?

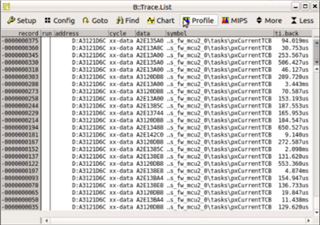

In other hand, and to complement info, I would like use PERF task in trace method, but it is not working, receiving errors of "virtual memory content, not valid at address unknown" that I suspect is for same issue, variables of current task are not accesible in runtime.

It would be great to see FreeRTOS resources at runtime

BR