So, I want to make some analysis with my L2 cache disabled. I'm running an U-boot environment, bare-metal, on my BeagleBone black and I'm trying to disable the cache following the steps provided on:

My code is something like this:

asm volatile("MRC p15, 0, %0, c1, c0, 0\t\n": "=r"(controlRegister)); //Retrieve Control Register

controlRegister = controlRegister & ~(1u << 2); //change Bit C to 0;

asm volatile ("MCR p15, 0, %0, c1, c0, 0\t\n" :: "r"(controlRegister)); //write new value

I know this is only the first step(disable C bit), but I'm having trouble accomplishing it. The problem is, when i try to write the new value and then check if it was write correctly, the value retrieved is 00000000.

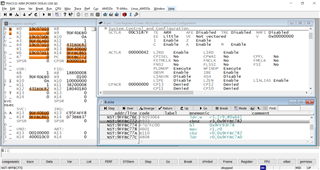

I've been trying to enter the supervisor mode without any success, but then I decided to look on my current operation mode accessing the CPSR and checking the [4-0] bits, as mentioned here . And, according to the CPSR I'm already on unsecured supervisor mode(10011), which seems to be a privileged mode. But I'm still unable to write effectively on Control Register (C1).

So I've tried to go from unsecured to secured mode, but according to the docs I can only access and change the NS-bit if I'm on a secure privileged mode.

My question is, how can I disable L2 cache, if I don't have a secure privileged mode access? For what i have searched the am335x does not allow TrustZone, which for what i understood is the equivalente of privileged secure mode.

So, there is no way to disable the L2 cache? Or I'm doing something wrong?

UPDATE: Adding some things that i've checked. On ARM's Documentation of Cortex-A8 it's said that I am supposed to be able to write on C1 register from an unsecure privileged mode (I'm on supervisor's mode, so that should be enough). When i try to write on C1 register, at this point, my program stays hanging and does not ends until the board restarts, the value that I'm trying to write is 0x00C50879, which is the equivalent of C and I bit disabled.

UPDATE 2: I don't know if it's relevant, but I'm using arm-none-eabi as my toolchain for compilling, and my code is being loaded on the address 0x80000000

Regards,

Lucas Cunha