Other Parts Discussed in Thread: TL5209

Good morning!

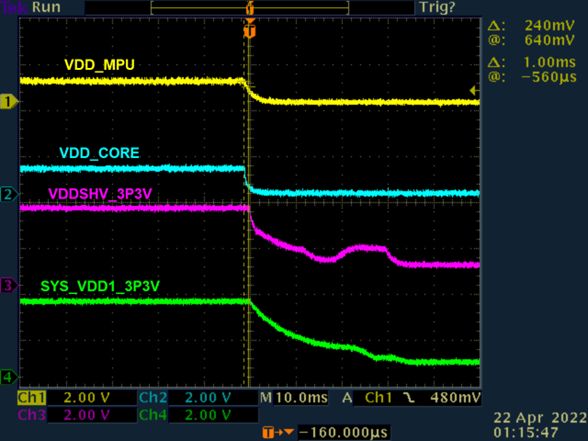

I am verifying a PCBA design with an Octavo OSD3358-512M-ICB C-SIP. This SOM contains a TPS65217C PMIC, TL5209 LDO, and an AM335x Sitara processor. LDO4 of the PMIC (a 3.3V LDO) powers VDDSHV 1, 3, 4, 5, and 6. VDDSHV 2 is powered by a 1.8V supply (LDO3). During the power down sequence, I'm seeing a little bump on the falling waveform of the supply that powers the five 3.3V VDDSHV pins. We have not satisfactorily tracked down the root cause of this behavior. That investigation is ongoing. In the meantime, I am hoping for clarity on whether this behavior is concerning? Will it damage the AM335x processor? Have you seen this behavior before? Thanks!

Pin legend:

- VDDSHV_3P3V -> TPS56217C LDO4

- SYS_VDD1_3P3V -> TL5209 Output

- VDD_CORE -> TPS56217C DCDC3

- VDD_MPU -> TPS56217C DCDC2

Note: I confirmed that registers 0x19 - 0x1E of the TPS56217C match the reset states for the variant of the IC.