Hi,

I am working on DMSS on the AM64X HS-FS board. Reading more about the Interrupt Aggregator implemented in DMSS, I have some questions.

It is a little confusing the different graphs that exist in the TRM (version 2.0). I share the photos in the following and explain what are the conflicts.

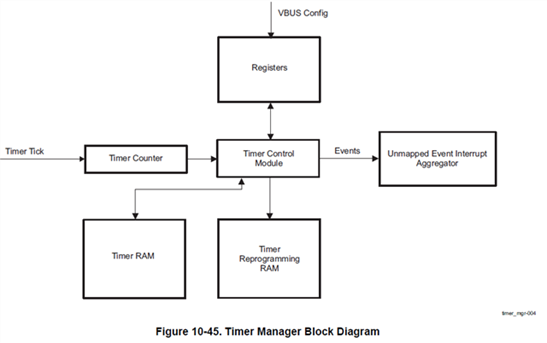

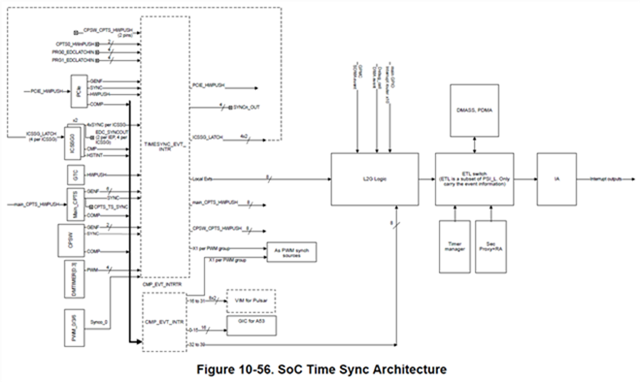

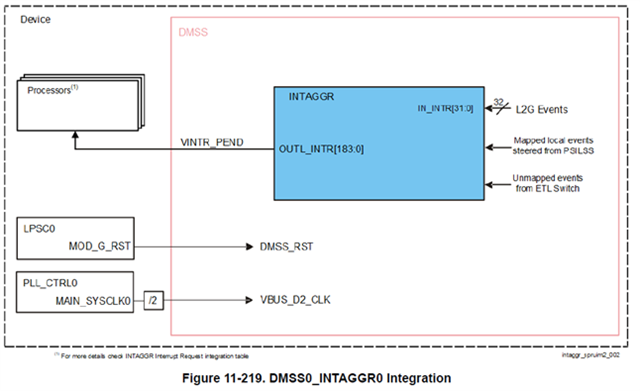

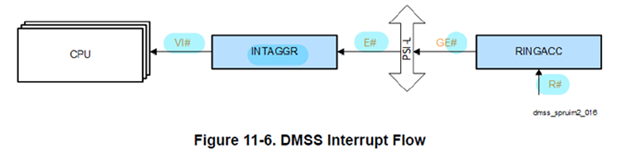

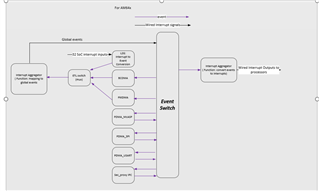

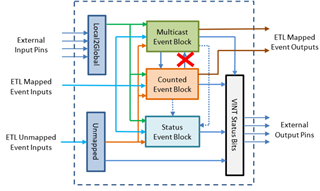

In figure 10-45 it shows that the events that are coming from Time Manager are unmapped events going to Interrupt Aggregator. In figure 11-219 it shows the unmapped events are coming from ETL to Interreupt aggregator (not directly), the same for figure 11-4.

In figure 11-4 it shows secure proxy events are coming from PSI-L, while in figure 10-56 it shows they are coming through ETL to Interrupt Aggregator.

In the other hand in the explanation of ETL it is mentioned it is a subset of PSI-L, a lane for transferring events. However in the figure 11-4 it is demonstrated as a separate block and in figure 11-219 events coming from PSI-L are differed from events coming from ETL; the first one is called Mapped Local events and the second one as unmapped events coming through ETL. Therefore, it seems they are not finally the same.

Also in figure 11-219 we see that the events going to Interrupt Aggregator are categorized into three category:

- L2G : However in figure 10-56 it shows that it first goes to ETL first then Interrupt Aggregator, so why it is not in the second category??

- Local mapped events steered from PSI-L: Is it that events coming through PSI-L are mapped and if not from PSI-L they are not mapped? What are the events that are in this category? Are they global?

- Local unmapped events coming from ETL. What are the events that are in this category? Are they global?

Each event category consist which events?

What is the difference of mapped and unmapped events?

L2G consists local events, however based on the name I believe the output of it should be global. So is it global events entering to Interrupt aggregator?

In the set of registers we have the following registers for interrupts:

- VINT registers that we have 184 of each register set.

- IMAP registers. we have 1536 of these registers. They contain the register number and the bit number of VINT that caused the interrupt to happen. How is that possible? We have 184 VINT register set, each having 64 bits, meaning 11776 possibility. It doesn’t match with the value 1536. Are these events the same as SEVI that is mentioned in TRM?

- L2G registers. These registers contain level/edge and global event index. What is this global event index? Is it part of the 184 x 64 possibilities? Or part of the 1536 registers?

- We have some global event mapping registers. I think we have 256 of them for case of AM64x. What are these global events? If we consider the three categories defined earlier, does it fall into any of them?

- The same thing for multi-cast events mapping registers.

- The same thing for unmapped mapping registers.

The architecture of Interrupt aggregator, its sources and destinations, definition of different event types defined (SEVI, GEVI, LEVI, MEVI, Mapped/Unmapped, L2G) are not clear.

On the other hand, in the API code there is a completely different definition. Events fall into categories of master, exclusive, shared. What is the relationship of these with the above registers and categories?