Other Parts Discussed in Thread: SYSCONFIG

Hello TI team,

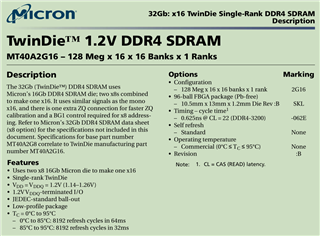

I am currently using our own PCB board, MPU model AM6234ATCGGAALW, DDR model MT40A2G16TBB-062E:F, which includes BG0 and BG1 signal pins. We used AM62x-DDRConfig_MT40A2G16.gel files containing BG0 and BG1 pins to debug DDR and found that DDR still cannot be accessed normally. By using a AM62x-DDRConfig_MT40A2G16_BG0_only.gel file that only contains BG0 pins, DDR can be accessed normally. Could you please analyze the reason? Thank you!

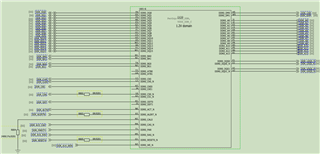

The schematic diagram of the custom board DDR section is as follows:

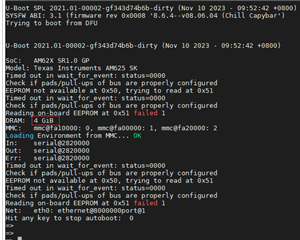

The logs that failed to access DDR using DDRConfig_MT40A2G16.gel files are as follows:

This is the file generated by sysconfig,Using two BG signals simultaneously and changing the density to 32Gb:

/cfs-file/__key/communityserver-discussions-components-files/791/3201.all.zip