Other Parts Discussed in Thread: TDA4VM

Hello,

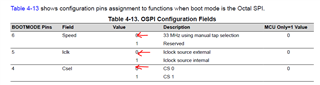

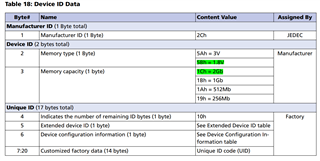

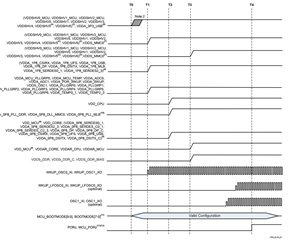

We are using the TDA4VM SOC in our design . The Boot configuration is set it as OSPI boot. The Boot flash device part# MT35XU02GCBA1G12-0AUT. While the module is powered ON, all the TDA SOC power supply voltages are generated from PMIC. The PMIC is able to release the reset signal as per the below drawing.

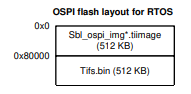

TI shared two flash file and flashed the file as per the below recommended location.

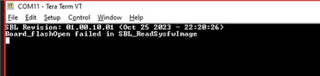

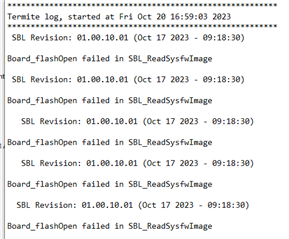

After loading the 2 files (not sure its flashed properly). But we verified the data stored in the device against the file and it seems to be fine. However, after loading the files, the UART log is below.

Is there anything that I need to look on to the Hardware to ensure everything is good for processor boot. And also, what could be the reason for this log.

Looking for your help in this regard.

Thanks-Arumugam