Other Parts Discussed in Thread: TDA4VL

Hi, experts ,

I am debugging tda4vl(sdk 0806) to boot from ospi and the following prompt error appears:

SPL: failed to boot from all boot devices

### ERROR ### Please RESET the board ###

I copied tiboot3. bin, tispl. bin, and u boot. img from Linux to OSPI flash, and the results read from OPSI flash are consistent with the source file.

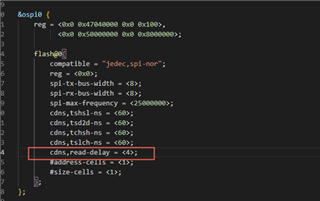

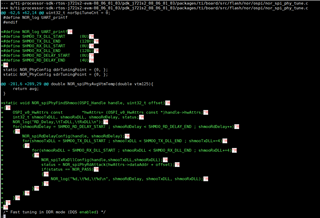

I added printing information to the ti-processor-sdk-linux-j721s2-evm-08_06_01_02/board-support/u-boot-2021.01+gitAUTOINC+62a9e51344-g62a9e51344/common/spl/spl_spi.c file and found that the spl_parse_image_header function returned an error value,

Please help me analyze this issue,thanks!

Best Regards,

Bing