Hello,

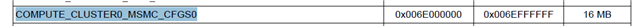

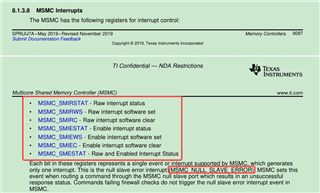

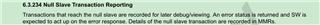

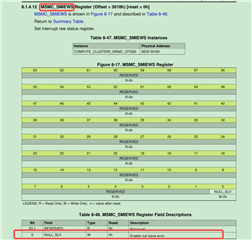

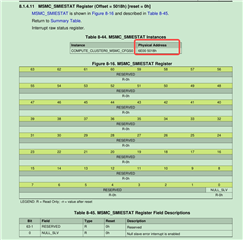

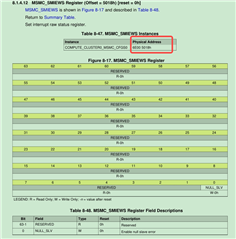

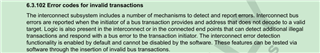

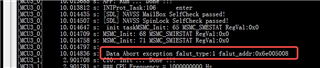

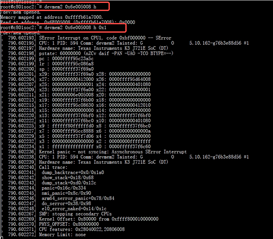

I failed to write to the MSMC NULL Slave function register because I registered an exception check and was prompted to write to address 0x6E005008 DataAbort. I would like to know how to solve this problem?

I tried to read and write the address using the devmem2 command on the A72 terminal, but found that the write failed.

Do I need to modify some content to initiate write operations on this register segment?