Part Number: TMS570LS0714

Other Parts Discussed in Thread: UNIFLASH, HALCOGEN,

Hello:

I want to make a BOOTLOADER for TMS570LS0714APZ. If I use the same program but different ICs, I will find that some can be programmed successfully, but some will fail. The following is the situation I tested.

1. Although adjusting SYS_CLK_FREQ can solve the problem of unsuccessful programming of different ICs, SYS_CLK_FREQ is fixed and cannot be adjusted for each IC during mass production, so this method cannot be used.

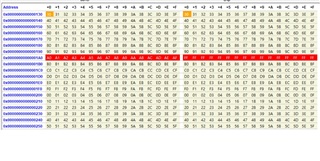

2. After the burning failed, read the burning content and found that there is a phenomenon, that is, the value of 16 BYTE is 0xFF every time, that is, the writing is not successful. It seems that the problem is Fapi_BlockProgram, in red font The two judgment conditions were added by me. They are improved but errors still occur.

uint32_t Fapi_BlockProgram( uint32_t Bank, uint32_t Flash_Address, uint32_t Data_Address, uint32_t SizeInBytes)

{

register uint32_t src = Data_Address;

register uint32_t dst = Flash_Address;

uint32_t bytes;

if (SizeInBytes < 16)

bytes = SizeInBytes;

else

bytes = 16;

if ((Fapi_initializeFlashBanks((uint32_t)SYS_CLK_FREQ)) == Fapi_Status_Success)

{

(void)Fapi_setActiveFlashBank((Fapi_FlashBankType)Bank);

(void)Fapi_enableMainBankSectors(0x0FFF); /* used for API 2.01*/

}

else {

return (1);

}

while( FAPI_CHECK_FSM_READY_BUSY != Fapi_Status_FsmReady );

while( FAPI_GET_FSM_STATUS != Fapi_Status_Success );

while( SizeInBytes > 0)

{

Fapi_issueProgrammingCommand((uint32_t *)dst,

(uint8_t *)src,

(uint32_t) bytes,

0,

0,

Fapi_AutoEccGeneration);

while( FAPI_CHECK_FSM_READY_BUSY == Fapi_Status_FsmBusy );

while(FAPI_GET_FSM_STATUS != Fapi_Status_Success);

while( FAPI_CHECK_FSM_READY_BUSY != Fapi_Status_FsmReady );

src += bytes;

dst += bytes;

SizeInBytes -= bytes;

if (SizeInBytes < 16)

{

bytes = SizeInBytes;

}

}

//status = Flash_Program_Check(Flash_Address, Data_Address, SizeInBytes);

return (0);

}

The questions I want to ask are the following:

1. How to confirm that the programming has been successful after burning 16 BYTEs each time?

2. If I execute Flash_Program_Check() every time after burning 16 BYTEs, what status do I need to set or check first, or do I need to delay it for a period of time?

3. Currently, every time I receive 2048 Byte data, I start burning. Is there a limit to the size of this temporary storage area? I ask this because I will continue to write after receiving 2048 Byte data until burning. After completion, receive the next 2048 Byte

4. What MHZ should be set to SYS_CLK_FREQ? It is currently set at 64MHZ.

5. Why does adjusting SYS_CLK_FREQ affect the success rate of programming (adjustment range 32MHz ~ 80MHz)

6. Why does Flash_Program_Check fail to execute after judging that Fapi_Status_Success has been successful?

Please, is there anyone who can help me? I would be very grateful.

PS:When reading the FLASH content when an error occurs, 16 consecutive BYTEs will be sent, but none of them are written.