We have the below queries related to TI EVM PROC141E3

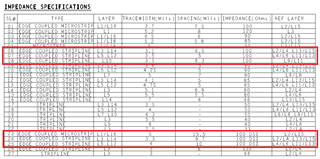

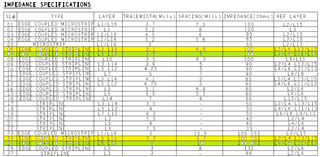

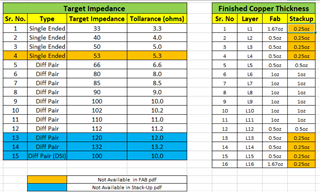

- We found a mismatch in the stack-up file (PROC141_STACKUP) & Fab drawing (PROC141E3_FAB) related to impedance & finished copper thickness. Below image for your reference purpose

- We found 132E impedance in the fab drawing but we are not able to find the same in the schematic. Please let us know for which application we are using 132E impedance.