Hi,

I have used this IBIS model sprm730c.ibs for the RGMII SI analysis for our AM6422 based design.

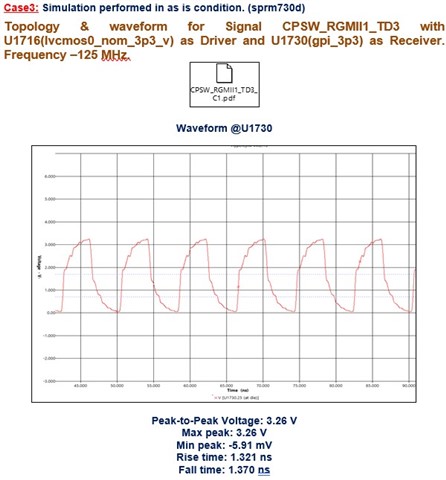

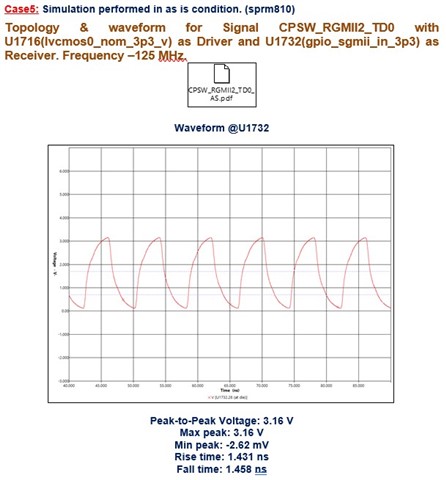

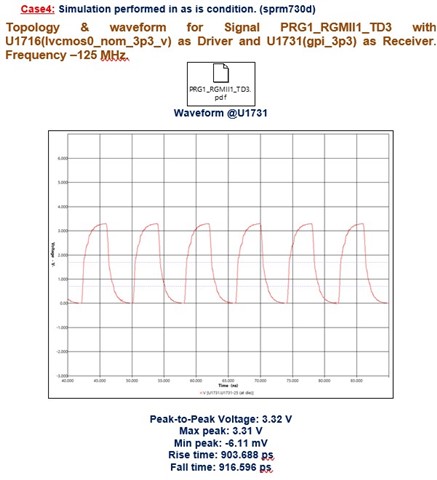

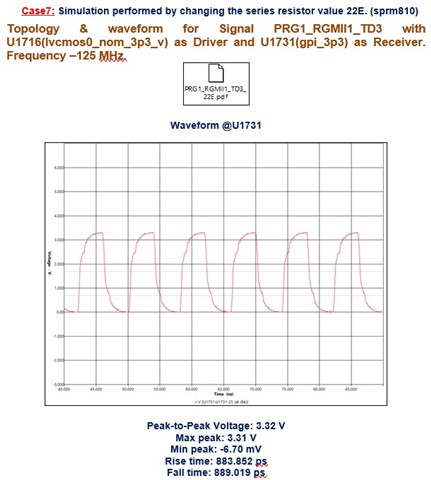

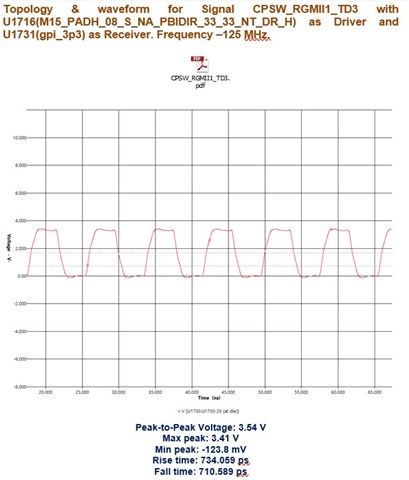

We are observing the rise time and fall time issues during the SI analysis and even monotonic failure in some test cases.

Refer below snapshots of the simulation.

Can you suggest any alternate IBIS model for the simulation or a way to increase the drive strength to meet the rise and fall times?

Thanks

Parthan