Other Parts Discussed in Thread: TIDA-01588, TIDA-01568

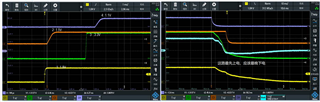

The discrete power solution sequence of AM335x, the power up sequence is fine, but the power down sequence violate the first up, last off sequence, the 1.5V(Orange) is later than 1.8V(Yellow) power down.

Does it impact AM335x longevity or reliability?

On this reference design used discrete power solution, power up sequence is ensured by EN, but how can it ensure power sequence?

https://www.ti.com/tool/TIDA-01568

Is there reference circuit to ensure power down sequence?