Other Parts Discussed in Thread: AM62A7

Hello,

I'd like to add other eth interface on AM62A7, but there's a little bit uncorrect somewhere. Please help me check it. The configuration details in DTS as below:

k3-am62-main.dtsi:

cpsw3g: ethernet@8000000 {

compatible = "ti,am642-cpsw-nuss";

#address-cells = <2>;

#size-cells = <2>;

reg = <0x0 0x8000000 0x0 0x200000>;

reg-names = "cpsw_nuss";

ranges = <0x0 0x0 0x0 0x8000000 0x0 0x200000>;

clocks = <&k3_clks 13 0>;

assigned-clocks = <&k3_clks 13 3>;

assigned-clock-parents = <&k3_clks 13 11>;

clock-names = "fck";

power-domains = <&k3_pds 13 TI_SCI_PD_EXCLUSIVE>;

dmas = <&main_pktdma 0xc600 15>,

<&main_pktdma 0xc601 15>,

<&main_pktdma 0xc602 15>,

<&main_pktdma 0xc603 15>,

<&main_pktdma 0xc604 15>,

<&main_pktdma 0xc605 15>,

<&main_pktdma 0xc606 15>,

<&main_pktdma 0xc607 15>,

<&main_pktdma 0x4600 15>;

dma-names = "tx0", "tx1", "tx2", "tx3", "tx4", "tx5", "tx6",

"tx7", "rx";

ethernet-ports {

address-cells = <2>;

size-cells = <2>;

cpsw_port1: port@1 {

reg = <1>;

ti,mac-only;

label = "port1";

phys = <&phy_gmii_sel 1>;

mac-address = [00 00 00 00 00 00];

ti,syscon-efuse = <&wkup_conf 0x200>;

};

cpsw_port2: port@2 {

reg = <2>;

ti,mac-only;

label = "port2";

phys = <&phy_gmii_sel 2>;

mac-address = [00 00 00 00 00 01];

};

};

cpsw3g_mdio: mdio@f00 {

compatible = "ti,cpsw-mdio","ti,davinci_mdio";

reg = <0x0 0xf00 0x0 0x100>;

#address-cells = <1>;

#size-cells = <0>;

clocks = <&k3_clks 13 0>;

clock-names = "fck";

bus_freq = <1000000>;

};

cpts@3d000 {

compatible = "ti,j721e-cpts";

reg = <0x0 0x3d000 0x0 0x400>;

clocks = <&k3_clks 13 3>;

clock-names = "cpts";

interrupts-extended = <&gic500 GIC_SPI 102 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "cpts";

ti,cpts-ext-ts-inputs = <4>;

ti,cpts-periodic-outputs = <2>;

};

};

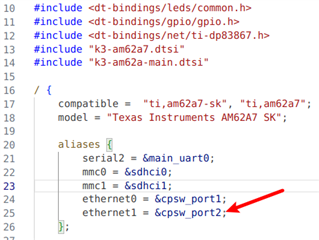

k3-am62a7-sk.dts:

main_rmii2_pins_default: main-rmii2-pins-default {

pinctrl-single,pins = <

AM62AX_IOPAD(0x184, PIN_INPUT, 0) /* (AA21) RMII2_RXD0 */

AM62AX_IOPAD(0x188, PIN_INPUT, 0) /* (Y20) RMII2_RXD1 */

AM62AX_IOPAD(0x180, PIN_INPUT, 0) /* (AA20) RMII2_REF_CLK*/

AM62AX_IOPAD(0x168, PIN_INPUT, 0) /*(AB19) RMII2_RX_CTL */

AM62AX_IOPAD(0x16C, PIN_INPUT, 0) /* (AA19) RMII2_TXD0 */

AM62AX_IOPAD(0x170, PIN_INPUT, 0) /* (Y18) RMII2_TXD1 */

AM62AX_IOPAD(0x164, PIN_INPUT, 0) /* (Y19) RMII2_TX_CTL */

>;

};

&cpsw3g {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&main_rgmii1_pins_default>;

pinctrl-1 = <&main_rmii2_pins_default>;

};

&cpsw_port1 {

status = "okay";//"disabled";//

phy-mode = "rgmii-rxid";

phy-handle = <&cpsw3g_phy0>;

};

&cpsw_port2 {

status = "okay";//"disabled";//

phy-mode = "rmii";

phy-handle = <&cpsw3g_phy1>;

};

&cpsw3g_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&main_mdio1_pins_default>;

cpsw3g_phy0: ethernet-phy@0 {

reg = <0>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

ti,min-output-impedance;

};

cpsw3g_phy1: ethernet-phy@3 {

reg = <0x3>; // first phy address

max-speed = <0x64>; //MII speed is 100M

};

};

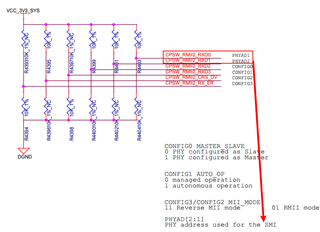

According to the Schematics, I think the phy address is 0x03:

the pin PHYAD1 and PHYAD2 are always level high, maybe the PHYAD = 0x3.

However, I found the below error when I run the modified version above:

I can't figure out the problem"SIOCSIFFLAGS: No such device". If I try to change the IP of eth1, it seems to be succeess.

So what should I do to solve this issue?