Hi experts:

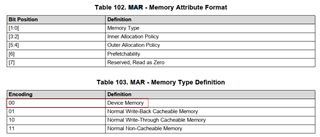

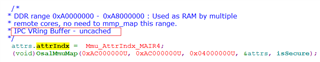

Is the MAIR register definition in C71 MMU the same as the definition in ARMv8? The value of the Mmu_MAIR4 variable in pdk_j784s4_08_06_00_31/packages/ti/csl/arch/c7x/src/mmu.c is initialized to 0x44, which corresponds to the no cache attribute( Normal memory, Inner &Outer Non-cacheable) if parsed according to ARMv8.

However, if you follow the MAR register analysis in the TI manual, it is the device memory(0x44 , 01000100b), which cannot correspond to the actual firmware configuration attributes.

MAIR initialize code:

Mmu_setMAIRAsm(4, Mmu_MAIR4);

-->

Mmu_setMAIRAsm

; .asmfunc

shld.l1 a4, 3, a4

shld.l1 a5, a4, a5

mvk64.l1 0xff, a6

mvc.s1 MAR_S, a7

shld.l1 a6, a4, a6

andnd.l1 a6, a7, a4

ord.l1 a4, a5, a4

mvc.s1 a4, MAR_S

mvc.s1 a4, MAR

|| ret.b1