Hello,

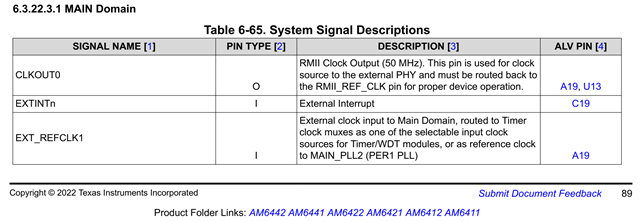

Looking at the AM6442 Datasheet in 6.3.22.3.1, it is said that the EXT_REFCLK1 Pin could be routed to the MAIN_PLL2

After searching through the whole Technical Reference Manual (SPRUIM2G MAY 2020 – REVISED JULY 2023), I cannot find how to do that.

If the MAIN_PLL2_REF_CLK can effectively be change to EXT_REF_CLK1, I would also like to know what is the current default frequency of this input.

Regards,

JS