Part Number: TDA4VM

Other Parts Discussed in Thread: TPS6594-Q1,

Question: In what condition may cause the "nRSTOUT" triggered & closed the PMIC buck output?

Condition:

1.This IC power are from "TPS6594" PMIC output.

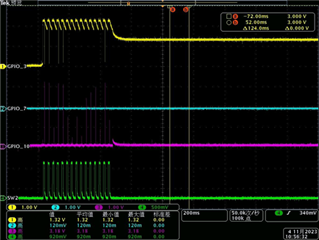

2.Some board can boot up successfully,but some couldn't. All of them with same PCBA、same layout、same materials.

Issue description:

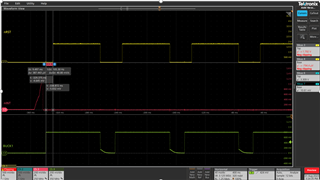

1.PMIC buck & LDO do not output power so Jacinto 7 can't boot up.

2.Found that PMIC try to output power ,but PMIC pin25 "nRSTOUT" triggered,so the power got off.