Hi,

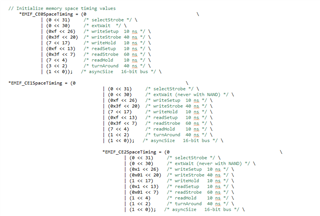

We are using TMS320C6655 DSP processor. We have tried with EMIF interface with DMA transfer as well as without DMA.

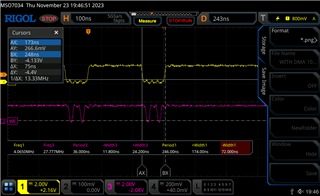

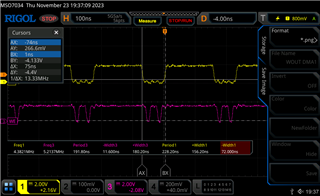

We are getting the data rate with maximum of 5 MHZ approximately whereas ,it should be 32 MHZ max according to the theoretical data.

I will share the probing images with frequency and width time period datas.

Please look into it and kindly support for the low data rate query.

Probing datas are with Chip select and write enable pin

Regards,

Thilak