Hello,

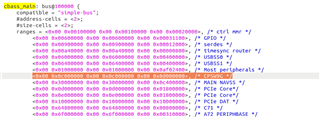

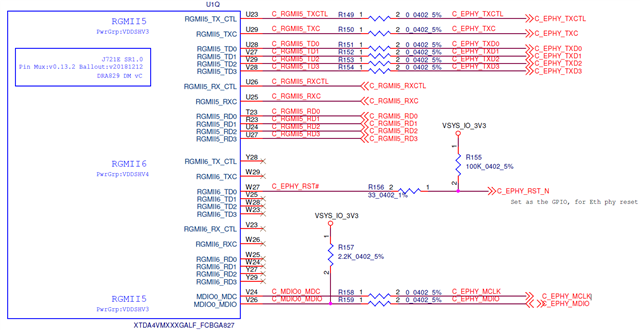

I have been testing J721e RGMII5 connect with a eth phy 88E1512. The hardware schematic is shown below:

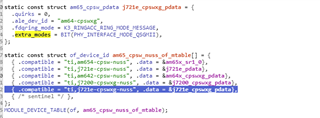

The original setting in DTS "k3-j721e-common-proc-board.dts" is using RGMII2, and it works fine on TI J7 EVM. Then, I attempted to modify to RGMII5 for my own board.

mcu_cpsw_pins_default: mcu-cpsw-pins-default {

pinctrl-single,pins = <

/*

J721E_WKUP_IOPAD(0x0058, PIN_OUTPUT, 0) MCU_RGMII1_TX_CTL

J721E_WKUP_IOPAD(0x005c, PIN_INPUT, 0) // MCU_RGMII1_RX_CTL

J721E_WKUP_IOPAD(0x0060, PIN_OUTPUT, 0) // MCU_RGMII1_TD3

J721E_WKUP_IOPAD(0x0064, PIN_OUTPUT, 0) // MCU_RGMII1_TD2

J721E_WKUP_IOPAD(0x0068, PIN_OUTPUT, 0) // MCU_RGMII1_TD1

J721E_WKUP_IOPAD(0x006c, PIN_OUTPUT, 0) // MCU_RGMII1_TD0

J721E_WKUP_IOPAD(0x0078, PIN_INPUT, 0) // MCU_RGMII1_RD3

J721E_WKUP_IOPAD(0x007c, PIN_INPUT, 0) // MCU_RGMII1_RD2

J721E_WKUP_IOPAD(0x0080, PIN_INPUT, 0) // MCU_RGMII1_RD1

J721E_WKUP_IOPAD(0x0084, PIN_INPUT, 0) // MCU_RGMII1_RD0

J721E_WKUP_IOPAD(0x0070, PIN_OUTPUT, 0) // MCU_RGMII1_TXC

J721E_WKUP_IOPAD(0x0074, PIN_INPUT, 0) // MCU_RGMII1_RXC

*/

J721E_WKUP_IOPAD(0x184, PIN_INPUT, 0) /* (T23) RGMII5_RD0 */

J721E_WKUP_IOPAD(0x180, PIN_INPUT, 0) /* (R23) RGMII5_RD1 */

J721E_WKUP_IOPAD(0x17c, PIN_INPUT, 0) /* (U24) RGMII5_RD2 */

J721E_WKUP_IOPAD(0x178, PIN_INPUT, 0) /* (U27) RGMII5_RD3 */

J721E_WKUP_IOPAD(0x174, PIN_INPUT, 0) /* (U25) RGMII5_RXC */

J721E_WKUP_IOPAD(0x15c, PIN_INPUT, 0) /* (U26) RGMII5_RX_CTL */

J721E_WKUP_IOPAD(0x16c, PIN_OUTPUT, 0) /* (U28) RGMII5_TD0 */

J721E_WKUP_IOPAD(0x168, PIN_OUTPUT, 0) /* (V27) RGMII5_TD1 */

J721E_WKUP_IOPAD(0x164, PIN_OUTPUT, 0) /* (V29) RGMII5_TD2 */

J721E_WKUP_IOPAD(0x160, PIN_OUTPUT, 0) /* (V28) RGMII5_TD3 */

J721E_WKUP_IOPAD(0x170, PIN_OUTPUT, 0) /* (U29) RGMII5_TXC */

J721E_WKUP_IOPAD(0x158, PIN_OUTPUT, 0) /* (U23) RGMII5_TX_CTL */

>;

};

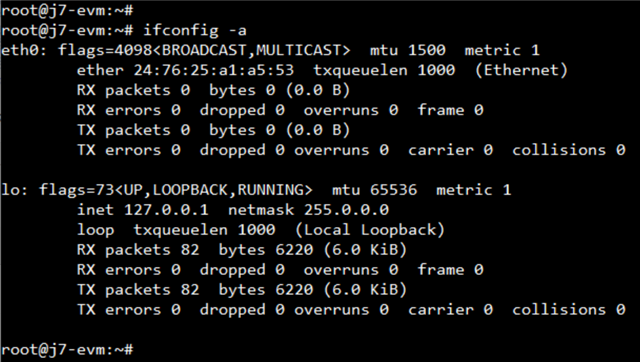

It shows eth0 with command "ifconfig -a".

But, when I wanted to set the IP for eth0 with command "ifconfig eth0 192.168.0.101", it showed error "No such device".

Does anyone know how to configure J721e RGMII5 with a eth phy 88E1512?

Thank you very much!!

Shawn