Part Number: AM3352

Other Parts Discussed in Thread: AMIC110

Hi experts

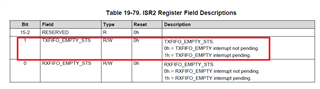

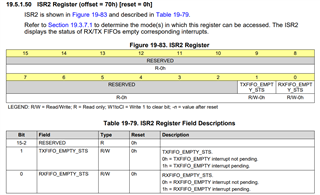

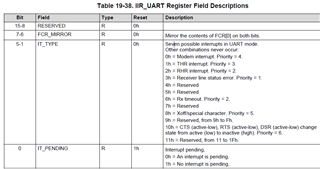

My customer currently uses [SCR.TXEMPTYCTLIT=1] for UART FIFO EMPTY interrupt.

However, according to actual measurements, in the case of high baud rate transmission, there is a very small probability (<1%) of interrupts causing ms-level delays;

So we want to ask, are there any other registers or other interrupts that can achieve the purpose of UART FIFO EMPTY interrupt?

Thanks!