Part Number: TDA4VM

Hello Champs,

HW: customer own board

SW: ti-processor-sdk-rtos-j721s2-evm-08_06_01_03

Customer is using TDA4VM ECO device. He is running SDL examples/rti/UC1 example in ti-processor-sdk-rtos-j721s2-evm-08_06_01_03.

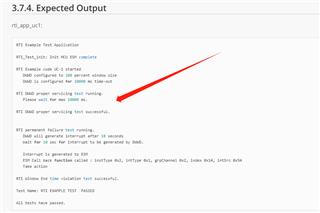

1. Enable watchdog, the watchdog timer doesn't exceed 10s, but the WD is triggered. It prompted "RTI DWWD proper servicing test failed."

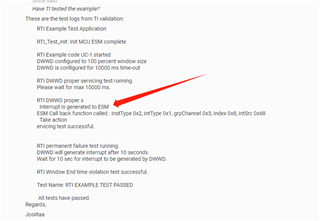

Have TI tested the example?

The log is below

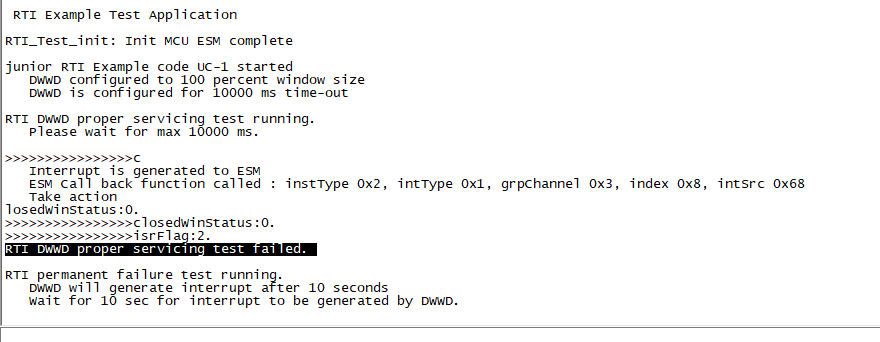

2. Modify the int32_t SDL_RTI_exampleTest(void) in sdl/examples/rti/UC1/sdl_rti_example.c as below

pConfig.SDL_RTI_dwwdReaction = RTI_DWWD_REACTION_GENERATE_NMI;------->pConfig.SDL_RTI_dwwdReaction = RTI_DWWD_REACTION_GENERATE_RESET;

The mcu is not reset.

The log is below:

Configure pConfig.SDL_RTI_dwwdReaction = RTI_DWWD_REACTION_GENERATE_RESET; will the watchdog reset the MCU? Is there some configurations missed?

Thanks

Regards

Shine