Hi,

I am designing a board with the TI AM4378 processor and I wanted to know what the eMMC Read hold time requirements are. The eMMC_Data[0:7] is connected to GPMC_AD[8:15]. The CLK and CMD are connected to MMC1_CLK and MMC1_CMD respectively.

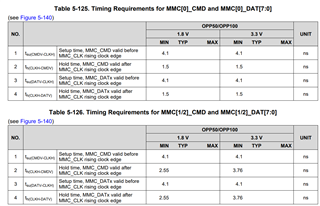

Per the datasheet there are two requirements for the MMC1 (3.3V):

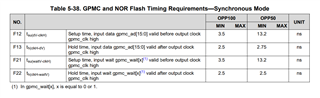

but for the GPMC requirements the hold-time is lower at 2.5 ns:

Which spec do we follow?

Thank you!